SIMM

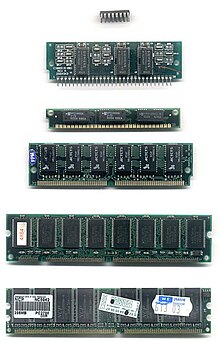

SIMM (sigles de Single In-line Memory Module), és un format per mòduls de memòria RAM que consisteixen en plaques de circuit imprès sobre les que es munten els integrats de memòria DRAM. Aquests mòduls s'insereix en sòcols sobre la placa base. Els contactes en ambdues cares estan interconnectats, aquesta és la major diferència respecte dels seus successors els DIMMs. Van ser molt populars des de principis dels 80 fins a finals dels 90, el format va ser estandarditzat per JEDEC sota el nombre JESD-21C.

Història de la memòria SIMM

[modifica]En els temps de l'ordinador domèstic i de l'ordinador personal, els circuits integrats de memòria (en general DIP de 14 o 16 pins) es soldaven o s'inserien en sòcols sobre la targeta mare com qualsevol altre component d'aquesta. Això suposava l'ús d'una àrea molt gran, ja que els integrats anaven col·locats un al costat de l'altre, a més que en el cas d'una fallada, la reparació era difícil o impossible condemnant tota la placa. L'actualització de memòria no es preveia en equips individuals, atès que el mercat de memòria no era tan comú. Amb el desenvolupament de noves targetes mare es van fer clares aquestes desavantatges i en un principi es van plantejar formats SIPP (no estàndard en computadors 80286) que van ser les primeres presentacions modulars de memòria RAM i l'antecedent directe de les SIMM.

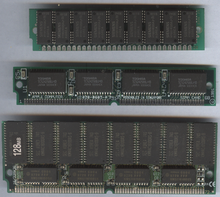

Skip Coppola va proposar durant la seva estada a IBM usar un SIPP de 3,5 polzades sense els pins que tan fàcilment es trencaven. IBM els adopta com a estàndard en la seva gamma IBM Personal System/2, i s'estenen a tots els compatibles amb CPU Intel 80286 i Intel 80386. És també adoptat per Apple per als seus Mac (el Macintosh IIfx usa uns SIMM no estàndard de 64 pins, i la VRAM dels Macintosh LC de 68), i més tardanament per Atari (en els Atari STe i Atari MEGA STe, encara que dels primers ha uns pocs amb SIPPs en comptes de SIMM) i Commodore per als Amiga (els fabricants d'ampliacions ho van fer molt abans). Es construeixen de 8 xips + una paritat (9 bits) o sense paritat (8 bits, amb l'estalvi d'un xip, però menor fiabilitat), majoritàriament de doble cara, i amb capacitats de 256 kB, 1 MB, 4 MB, 16 MB. En alguns sistemes havien usar-se a parells, ja que cada banc de memòria estava integrat per dos mòduls.

L'aparició del Intel 80486 porta també el pas al nou format de 108 mm (4,25 polzades) i 72 pins. Això era degut al fet que en un 386/486 era necessari instal·lar 4 SIMM amb 30 pins per completar una bancada de memòria. Aquesta bancada podia substituir-se per un sol DIMM de 72 pins (dos en els equips Pentium) el que va permetre conservar el factor de forma 'Baby AT' a les plaques mare malgrat quadruplicar la capacitat de memòria. Es fabriquen amb memòria EDO/FPM/ECC i capacitats d'1 MB, 2 MB, 4 MB, 8 MB, 16 MB, 32 MB, 64 MB, 128 MB (aquests últims només usats en servidors).

El factor de forma de memòria RAM utilitzat en PC és una presentació dels mòduls de memòria que va ser utilitzat en els sistemes els busos de dades eren de 32 bits o menys. A partir de l'ús de busos de 64 bits han estat reemplaçats pels DIMM, que són el nou factor de forma estàndard per als mòduls de memòria usats en ordinadors personals, en els que la capacitat d'emmagatzematge ja es mesura en gigabytes.

Un PC s'usa tant memòria de nou bits (vuit bits per a dades i un bit per revisió, o control, de paritat, en 9 xips de memòria RAM dinàmica) com a memòria de vuit bits sense paritat.

Patillatjes

[modifica]SIMM de 30 contactes

[modifica]| + SI | ||

| 6 | DQ1 | Data 1 |

| 7 | A2 | Address 2 |

| 8 | A3 | Address 3 |

| 9 | GND | Ground |

| 10 | DQ2 | Data febrer |

| 11 | A4 | Address 4 |

| 12 | A5 | Address 5 |

| 13 | DQ3 | Data març |

| 14 | A6 | Address 6 |

| 15 | A7 | Address 7 |

| 16 | DQ4 | Data abril |

| 17 | A8 | Address 8 |

| 18 | A9 | Address setembre |

| 19 | A10 | Address 10 |

| 26 | QP | Data Parity Out |

| 27 | / RES | Row Address Strobe |

| 28 | / CASP | Column Address Strobe Parity |

| 29 | DP | Data Parity In |

| 30 | VCC | +5 VDC |

- QP i DP no està connectats en els models sense paritat

- A9 no està connectat en els de 256 kB.

- A10 no està connectat en els de 256 kB i 1 MB.

- A11 no està connectat en els de 256 kB, 1 MB i 4 MB.

SIMM de 72 contactes

[modifica]| Pin # | Non-Parity | Parity | Signal Description |

|---|---|---|---|

| 1 | VSS | VSS | Ground |

| 2 | dq0 | dq0 | Data 0 |

| 3 | DQ1 | DQ1 | Data 1 |

| 4 | DQ2 | DQ2 | Data febrer |

| 5 | DQ3 | DQ3 | Data març |

| 6 | DQ4 | DQ4 | Data abril |

| 7 | DQ5 | DQ5 | Data maig |

| 8 | DQ6 | DQ6 | Data 6 |

| 9 | DQ7 | DQ7 | Data juliol |

| 10 | VCC | VCC | +5 VDC |

| 11 | PD1 | PD1 | Presence Detect 1 |

| 12 | A0 | A0 | Address 0 |

| 13 | A1 | A1 | Address 1 |

| 14 | A2 | A2 | Address 2 |

| 15 | A3 | A3 | Address 3 |

| 16 | A4 | A4 | Address 4 |

| 17 | A5 | A5 | Address 5 |

| 18 | A6 | A6 | Address 6 |

| 19 | A10 | A10 | Address 10 |

| 20 | n/c | PQ8 | Data 8 (Parity 1) |

| 21 | DQ9 | DQ9 | Data setembre |

| 22 | DQ10 | DQ10 | Data 10 |

| 23 | DQ11 | DQ11 | Data 11 |

| 24 | DQ12 | DQ12 | Data 12 |

| 25 | DQ13 | DQ13 | Data 13 |

| 26 | DQ14 | DQ14 | Data 14 |

| 27 | DQ15 | DQ15 | Data 15 |

| 28 | A7 | A7 | Address 7 |

| 29 | A11 | A11 | Address 11 |

| 30 | VCC | VCC | +5 VDC |

| 31 | A8 | A8 | Address 8 |

| 32 | A9 | A9 | Address setembre |

| 33 | / RAS3 | RAS3 | Row Address Strobe 3 |

| 34 | / RAS2 | RAS2 | Row Address Strobe 2 |

| 35 | DQ16 | DQ16 | Data 16 |

| 36 | n/c | PQ17 | Data 17 (Parity 2) |

| 37 | DQ18 | DQ18 | Data 18 |

| 38 | DQ19 | DQ19 | Data 19 |

| 39 | VSS | VSS | Ground |

| 40 | / CAS0 | CAS0 | Column Address Strobe 0 |

| 41 | / CAS2 | CAS2 | Column Address Strobe 2 |

| 42 | / CAS3 | CAS3 | Column Address Strobe 3 |

| 43 | / CAS1 | CAS1 | Column Address Strobe 1 |

| 44 | / RAS0 | RAS0 | Row Address Strobe 0 |

| 45 | / RAS1 | RAS1 | Row Address Strobe 1 |

| 46 | A12 | A12 | Address 12 |

| 47 | / WE | WE | Read/Write |

| 48 | A13 | A13 | Address 13 |

| 49 | DQ20 | DQ20 | Data 20 |

| 50 | DQ21 | DQ21 | Data 21 |

| 51 | DQ22 | DQ22 | Data 22 |

| 52 | DQ23 | DQ23 | Data 23 |

| 53 | DQ24 | DQ24 | Data 24 |

| 54 | DQ25 | DQ25 | Data 25 |

| 55 | n / c | PQ26 | Data 26 (Parity 3) |

| 56 | DQ27 | DQ27 | Data 27 |

| 57 | DQ28 | DQ28 | Data 28 |

| 58 | DQ29 | DQ29 | Data 29 |

| 59 | DQ31 | DQ31 | Data 31 |

| 60 | DQ30 | DQ30 | Data 30 |

| 61 | VCC | VCC | +5 VDC |

| 62 | DQ32 | DQ32 | Data 32 |

| 63 | DQ33 | DQ33 | Data 33 |

| 64 | DQ34 | DQ34 | Data 34 |

| 65 | n/c | PQ35 | Data 35 (Parity 4) |

| 66 | PD2 | PD2 | Presence Detect 2 |

| 67 | PD3 | PD3 | Presence Detect 3 |

| 68 | PD4 | PD4 | Presence Detect 4 |

| 69 | PD5 | PD5 | Presence Detect 5 |

| 70 | PD6 | PD6 | Presence Detect 6 |

| 71 | PD7 | PD7 | Presence Detect 7 |

| 72 | VSS | VSS | Ground |