SPARC-Architektur

Van Wikipedia, de gratis encyclopedie

Van Wikipedia, de gratis encyclopedie

Die SPARC-Architektur (Scalable Processor ARChitecture) ist eine Mikroprozessorarchitektur, die hauptsächlich in Produkten von Oracle Verwendung findet. Daneben gibt es noch andere Hersteller, wie zum Beispiel Fujitsu Technology Solutions (ehemals Fujitsu Siemens Computers).

Geschichte[Bearbeiten | Quelltext bearbeiten]

Sun Microsystems entwickelte ab 1985 und vermarktete ab 1987 die ersten Generationen von SPARC-Prozessoren. 1989 wurde die nicht gewinnorientierte Organisation SPARC International gegründet, als Anlaufstelle für die Weiterentwicklung der offenen SPARC-Architektur. SPARC International ist der Rechteinhaber an der Marke SPARC.[1]

Sun war zum Zeitpunkt der Entwicklung bereits der zweitgrößte Hersteller von Workstations mit dem Betriebssystem Unix (Marktanteile 1985: Apollo Computer 41 %, Sun 21 %). Mit dem SPARC-Prozessor wollte das Unternehmen, wie damals viele Hersteller von Workstations, eine RISC-Prozessorarchitektur schaffen, die die 68020- sowie die i386-Roadrunner-Prozessoren ablösen und viele Jahre lang konkurrenzfähig bleiben sollte. Die Prozessoren wurden von anderen Herstellern wie Texas Instruments oder Fujitsu gefertigt.

Sun brachte mit seiner Sun-4-Baureihe viele Workstations und Server heraus, die den SPARC-Prozessor verwendeten. Aber auch Fujitsu baute bis in das Jahr 2005 noch SPARC-Prozessoren in ihre PrimePower-Systeme ein. Außer SunOS bzw. Solaris können auf SPARC-Systemen auch Linux oder die modernen BSD-Varianten eingesetzt werden. 1995 wurde die ursprüngliche 32-Bit-Architektur auf 64-Bit erweitert und unter dem Namen UltraSparc vermarktet. Diese Architektur hat neben zusätzlichen Einheiten eine tiefere Pipeline und einige einfache SIMD-Befehle (Visual Instruction Set (VIS)). Der Ultrasparc-Standard hat mehrere Hauptversionen, die derzeit aktuelle Version ist UltraSparc T5.

Herausragende Eigenschaft der Architektur ist ein Registersatz (register file), der ursprünglich aus 128 32-Bit-Registern bestand. Die CPU kann nur auf einen Teil davon, normalerweise 32, direkt zugreifen. 24 davon sieht die CPU in einem Fenster, das per Software verschoben werden kann (→ Registerfenster). Dadurch können Argumente und Ergebnisse von Unterprogrammen ohne Umkopieren von Registern durch Verschieben des Fensters übergeben werden.

Die Gleitkommaeinheit kann als 32-faches 32-Bit-Register mit einfacher Genauigkeit, 16-faches 64-Bit-Register mit doppelter Genauigkeit oder 8-faches 128-Bit-Register mit vierfacher Genauigkeit verwendet werden.

Die aktuellen Versionen sind 32-Bit V8 und 64-Bit V9. Die SPARC V8 ist vollständig Big Endian. Die SPARC V9 benutzt Instruktionen im Big-Endian-Format, unterstützt jedoch beide Byte-Reihenfolgen für Datenwerte. Dies kann sowohl auf Instruktionsebene durch Verwendung spezieller Befehle als auch für ganze Speicherbereiche mittels einer MMU-Einstellung umgeschaltet werden. Letzteres wird insbesondere dann verwendet, wenn auf Speicherbereiche von Geräten zugegriffen werden muss, wie zum Beispiel den als Little Endian festgelegten PCI-Bus.

Eine einfache Version eines SPARC-Prozessors namens LEON1 in der Hardware-Beschreibungssprache VHDL ist von der ESA frei erhältlich. Sowohl das Design des UltraSPARC T1 als auch das des UltraSPARC T2 wurden 2006 bzw. 2007 unter der Open-Source-Lizenz GPL über das Projekt OpenSPARC veröffentlicht[2] und können dort heruntergeladen werden.[3] Auch das Design der Sun Microsparc ist seit Mitte 1990 im Quellcode veröffentlicht und frei nutzbar.

Es gibt auch eine Reihe Microcontroller-Implementierungen (zum Beispiel von Hitachi), die jedoch teilweise einen komprimierten Maschinencode besitzen und deshalb nicht binärkompatibel sind.

Seit der Übernahme von Sun Microsystems durch Oracle gehört mittlerweile der SPARC zu Oracle. 2017 zog sich Oracle aus der Entwicklung von SPARC zurück.[4]

SPARC64 ist ein eingetragenes Warenzeichen von SPARC International, Inc., und ist exklusiv an Fujitsu Limited vergeben.[5]

Im März 2022 veröffentlichte Fujitsu eine neue Roadmap für die Mainframe- und SPARC Server, daraus geht hervor, dass es bis ins Jahr 2035 keine Weiterentwicklung mehr geben wird, nur noch Verbesserungen, 2029 der Verkauf eingestellt und ab März 2035 der Support eingestellt wird.[6]

Modelle[Bearbeiten | Quelltext bearbeiten]

verschiedene Implementierungen der SPARC-Architektur, unter anderem Suns erfolgreicher SuperSPARC und UltraSPARC-I:

| Sun SPARC-Mikroprozessor-Spezifikation | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Modell | Frequenz [MHz] | Architektur Version | Jahr | Prozess [µm] | Transistoren [Millionen] | Kern- abmessung [mm²] | IO Pins | Aufnahme [W] | Spannung [V] | L1 Dcache [k] | L1 Icache [k] | L2 Cache [k] | L3 Cache [k] |

| SPARC | 14,28–40 | V7 | 1987–1992 | 0,8–1,3 | ~0,1–1,8 | — | 160–256 | — | — | 0–128 | kein | kein | |

| microSPARC I | 50 | V8 | 1992 | 0,8 | 0,8 | 225 | 288 | 2,5 | 5 | 4 | 2 | kein | kein |

| SuperSPARC I | 33–65 | V8 | 1992 | 0,8 | 3,1 | 256 | 293 | 14,3 | 5 | 16 | 20 | 1024 | kein |

| microSPARC II | 60–125 | V8 | 1992 | 0,5 | 2,3 | 233 | 321 | 5 | 3,3 | 8 | 16 | kein | kein |

| SuperSPARC II | 75–90 | V8 | 1994 | 0,8 | 3,1 | 299 | — | 16 | — | 16 | 20 | 2048 | kein |

| TurboSPARC | 170–180 | V8 | 1995 | 0,35 | — | — | — | 7 | — | 16 | 16 | 1024 | kein |

| UltraSPARC I | 140–200 | V9 | 1995 | 0,5 | 5,2 | 315 | 521 | 30 | 3,3 | 16 | 16 | 1024 | kein |

| UltraSPARC II | 250–480 | V9 | 1997 | 0,25 | 5,4 | 156 | 521 | 21 | 3,3 | 16 | 16 | 8192 | kein |

| UltraSPARC IIi | 270–650 | V9 | 1998 | 0,25 | 5,75 | 148 | 370 | 17,6 | 1,7 | 16 | 16 | 2048 | kein |

| UltraSPARC IIe | 400–500 | V9 | 2000 | 0,18 | 5,4 | — | 370 | 13 | 1,7 | 16 | 16 | 256 | kein |

| UltraSPARC III | 600–1200 | V9 | 2001 | 0,13 | 29 | 330 | 1368 | 53 | 1,6 | 64 | 32 | 8192 | kein |

| UltraSPARC IIIi | 1064–1600 | V9 | 2003 | 0,13 | 87,5 | 206 | 959 | 52 | 1,3 | 64 | 32 | 1024 | kein |

| UltraSPARC IV | 1050–1350 | V9 | 2004 | 0,13 | 66 | 356 | 1368 | 108 | 1,35 | 64 | 32 | 16384 | kein |

| UltraSPARC IV+ | 1500–2100 | V9 | 2005 | 0,09 | 295 | 336 | 1368 | 90 | 1,1 | 64 | 64 | 2048 | 32768 |

| UltraSPARC T1 | 1000–1400 | V9 | 2005 | 0,09 | 279 | 379 | 1934 | 79 | 1,3 | 8 | 16 | 3072 | kein |

| UltraSPARC T2 | 900–1400 | V9 | 2007 | 0,065 | 503 | 342 | 1831 | 95 | 1,2 | 8 | 16 | 4096 | kein |

| UltraSPARC T2+ | 1200–1600 | UA2007 | 2008 | 0,065 | 503 | 342 | 1831 | - | - | 8 | 16 | 4096 | kein |

| UltraSPARC T3 | 1650 | UA2007 | 2010 | 0,04 | - | 371 | - | 139 | - | 8 | 16 | 6144 | kein |

| UltraSPARC T4 | 2850-3000 | OSA2011 | 2011 | 0,04 | 855 | 403 | - | 240 | - | 16x8 | 16x8 | 128x8 | kein |

| UltraSPARC T5 | 3600 | OSA2011 | 2013 | 0,028 | 1500 | 478 | - | - | - | 16x16 | 16x16 | 128x16 | 8192 |

| Ross/Bridgepoint SPARC-Mikroprozessor-Spezifikation | |||||||||||||

| HyperSPARC A | 55–80 | V8 | 1993 | 0,5 | 1,5 | — | — | — | 5 | kein | 8 | 256 | kein |

| HyperSPARC B | 90–125 | V8 | 1995 | 0,4 | 1,5 | — | — | 25 | 5 | kein | 8 | 256 | kein |

| HyperSPARC C | 110–166 | V8 | 1995 | 0,35 | 1,5 | — | — | 45,5 | 5 | kein | 8 | 1024 | kein |

| HyperSPARC D | 180–200 | V8 | 1995 | 0,35 | 1,7 | — | — | — | 5 | 16 | 16 | 1024 | kein |

| Sun/Fujitsu SPARC64-Prozessoren | |||||||||||||

| SPARC64 V | 1350–2160 | V9 | 2004 | 0,13 | 191 | 290 | 269 | 40 | 1,2 | 128 | 128 | 2048 | kein |

| SPARC64 VI | 2150–2400 | V9 | 2007 | 0,09 | 540 | 422 | — | 120 | — | 128 | 128 | 6144 | kein |

| SPARC64 VII | 2700 | V9 | 2008 | 0,065 | 600 | 445 | — | 135 | — | 64 | 64 | 6144 | kein |

| SPARC64 VIII | 2000 | V9 | 2009 | 0,045 | 760 | 513 | — | 58 | — | 32 | 32 | 4096 | kein |

| SPARC64 X[7][8] | 3000 | V9 | 2013 | - | - | - | — | - | — | - | 32 | - | 24576 |

| SPARC64 XII[9] | 3900-4250 | V9 | 2017 | 0,02 | 5500[10] | 64 | 64 | 512 | 32768[10] | ||||

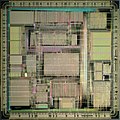

- „Die“ eines TI microSPARC I

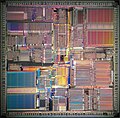

- „Die“ eines Sun SuperSPARC II

- „Die“ eines Ross hyperSPARC RT625A

Siehe auch[Bearbeiten | Quelltext bearbeiten]

Weblinks[Bearbeiten | Quelltext bearbeiten]

- LEON2 und LEON3 SPARC VHDL-Modelle (unter LGPL-Lizenz)

- SPARC-Prozessoren: Bilder und Beschreibungen auf cpu-collection.de

- OpenSPARC Overview (OpenSPARC-Projektseite)

- Fujitsu SPARC Servers (englisch)

- Multi-core multi-thread processor SPARC64 VI (englisch)

- MPF: Fujitsu präsentiert neue SPARC64 V-CPU

- SPARC64 X/X+ SpezifikationSPARC64 X/X+ Spezifikation

- Fujitsu SPARC XII Spezifikation

Einzelnachweise[Bearbeiten | Quelltext bearbeiten]

- ↑ Trademark Law | SPARC International, Inc. Abgerufen am 30. Januar 2021 (amerikanisches Englisch).

- ↑ Jens Ihlenfeld: OpenSPARC T2: Sun stellt UltraSPARC T2 unter die GPL. In: Golem.de. 12. Dezember 2007, abgerufen am 2. April 2017.

- ↑ OpenSPARC Overview. (deutsch: OpenSPARC-Projektseite). Oracle, abgerufen am 30. Dezember 2022 (englisch).

- ↑ Andy Patrizio: Game over for Solaris and SPARC? 23. Januar 2017, abgerufen am 23. April 2022 (englisch).

- ↑ Fujitsu Limited: SPARC64™ XII Specification. (fujitsu.com [PDF]).

- ↑ Fujitsu SPARC Servers Roadmap. Abgerufen am 23. April 2022.

- ↑ Fujitsu launches 'Athena' Sparc64-X servers in Japan. the register, abgerufen am 27. Februar 2013 (englisch).

- ↑ Fujitsu Limited: SPARC64™ X / X+ Specification. Nakahara-ku, Kawasaki 27. Januar 2015.

- ↑ SPARC64 XII – Fujitsu – WikiChip. Abgerufen am 30. Januar 2021 (englisch).

- ↑ a b Andreas Schilling: Fujitsu SPARC64 XII – 12 Kerne und 8 Threads pro Kern für Datenbanken. Abgerufen am 12. April 2021.