UltraSPARC

| UltraSPARC | ||

|---|---|---|

| ||

| Información | ||

| Desarrollador | Sun Microsystems | |

| Fabricante | Texas Instruments | |

| Datos técnicos | ||

| Conjunto de instrucciones | SPARC V9 | |

El UltraSPARC es un microprocesador desarrollado por Sun Microsystems y fabricado por Texas Instruments, introducido a mediados de 1995. Es el primer microprocesador de Sun en implementar la arquitectura de conjunto de instrucciones SPARC V9 de 64 bits (ISA). Marc Tremblay fue un co-microarquitecto.

Microarquitectura

[editar]El UltraSPARC es un microprocesador superescalar four-issue que ejecuta las instrucciones fuera de orden. Tiene una tubería de enteros de nueve etapas.

Unidades funcionales

[editar]Las unidades de ejecución se simplificaron en relación con el SuperSPARC para lograr frecuencias de reloj más altas; un ejemplo de una simplificación es que las ALU no se conectan en cascada, a diferencia del SuperSPARC, para evitar la restricción de la frecuencia del reloj.

El archivo de registro de tipo entero tiene 32 entradas de 64 bits. Como SPARC ISA usa ventanas de registro, de las cuales UltraSPARC tiene ocho, el número real de registros es 144. El archivo de registro tiene siete puertos de lectura y tres puertos de escritura. El archivo de registro de enteros proporciona registros a dos unidades lógicas aritméticas y la unidad de carga/almacenamiento. Las dos ALU pueden ejecutar instrucciones aritméticas, lógicas y de desplazamiento, pero solo una puede ejecutar instrucciones de multiplicación y división.

La unidad de punto flotante consta de cinco unidades funcionales. Uno ejecuta sumas y restas de punto flotante, uno multiplica, otro divide, y otro más calcula raíces cuadradas. Dos unidades son para ejecutar instrucciones SIMD definidas por el conjunto de instrucciones visuales (VIS). El archivo de registro de punto flotante contiene treinta y dos registros de 64 bits. Tiene cinco puertos de lectura y tres puertos de escritura.

Caché

[editar]El UltraSPARC tiene dos niveles de caché, primario y secundario. Hay dos cachés primarios, uno para instrucciones y otro para datos. Ambos tienen una capacidad de 16 KB.

El UltraSPARC requería un caché secundario externo obligatorio. El caché está unificado, tiene una capacidad de 512 KB a 4 MB y se asigna directamente. Puede devolver datos en un solo ciclo. La memoria caché externa se implementa con SRAM síncronas sincronizadas a la misma frecuencia que el microprocesador, ya que los ratios no fueron soportadas. Se accede a través del bus de datos.

Manufactura

[editar]Contenía 3,8 millones de transistores. Fue fabricado en el proceso EPIC-3 de Texas Instruments, un proceso complementario de 0,5 µm de metal-óxido-semiconductor (CMOS) con cuatro niveles de metal. El UltraSPARC no se fabricó en un proceso BiCMOS ya que Texas Instruments afirmó que no se ajustaba bien a los procesos de 0.5 µm y ofrecía poca mejora en el rendimiento. El proceso se perfeccionó en el procesador de señal digital MVP (DSP) de TI con algunas características que faltan, como tres niveles de metal en lugar de cuatro y un tamaño de función de 0.55, antes de que se usara para fabricar el UltraSPARC para evitar una repetición de los problemas de fabricación encontrados en los SuperSPARC.

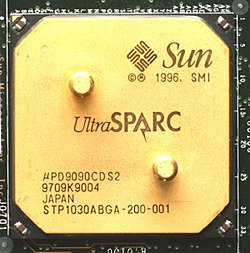

Empaquetado

[editar]El UltraSPARC está empaquetado en una matriz de rejilla de bola de plástico de 521 contactos (PBGA).

Procesadores relacionados

[editar]Referencias

[editar]- Greenley, D. et al. (1995). "UltraSPARC: la SPARC superscalar de 64 bits de próxima generación". Actas de Compcon '95 : pp. 442 – 451.

- Gwennap, Linley (3 de octubre de 1994). "UltraSparc desata rendimiento SPARC". Informe del microprocesador, volumen 8, número 13.

- Gwennap, Linley (5 de diciembre de 1994). "UltraSparc agrega instrucciones multimedia". Informe del microprocesador .