Serial communication

This article needs additional citations for verification. (August 2019) |

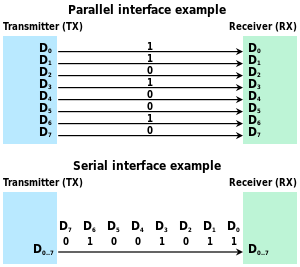

In telecommunication and data transmission, serial communication is the process of sending data one bit at a time, sequentially, over a communication channel or computer bus. This is in contrast to parallel communication, where several bits are sent as a whole, on a link with several parallel channels.

Serial communication is used for all long-haul communication and most computer networks, where the cost of cable and synchronization difficulties make parallel communication impractical. Serial computer buses have become more common even at shorter distances, as improved signal integrity and transmission speeds in newer serial technologies have begun to outweigh the parallel bus's advantage of simplicity (no need for serializer and deserializer, or SerDes) and to outstrip its disadvantages (clock skew, interconnect density). The migration from PCI to PCI Express (PCIe) is an example.

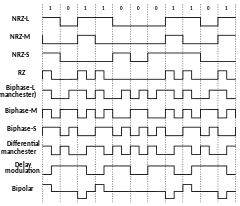

Modern high speed serial interfaces such as PCIe[2][3][4] send data several bits at a time using modulation/encoding techniques such as PAM4 which groups 2 bits at a time into a single symbol, and several symbols are still sent one at the time. This replaces PAM2 or non return to zero (NRZ) which only sends one bit at a time, or in other words one bit per symbol.[5][6][7][8][9][10][11][12] The symbols are sent at a speed known as the symbol rate or the baud rate.[13][14][15][16]

Cables

[edit]Many serial communication systems were originally designed to transfer data over relatively large distances through some sort of data cable.

Practically all long-distance communication transmits data one bit at a time, rather than in parallel, because it reduces the cost of the cable. The cables that carry this data (other than "the" serial cable) and the computer ports they plug into are usually referred to with a more specific name, to reduce confusion.

Keyboard and mouse cables and ports are almost invariably serial—such as PS/2 port, Apple Desktop Bus and USB.

The cables that carry digital video are also mostly serial—such as coax cable plugged into a HD-SDI port, a webcam plugged into a USB port or FireWire port, Ethernet cable connecting an IP camera to a Power over Ethernet port, FPD-Link, digital telephone lines (ex. ISDN), etc.

Other such cables and ports, transmitting data one bit at a time, include Serial ATA, Serial SCSI, Ethernet cable plugged into Ethernet ports, the Display Data Channel using previously reserved pins of the VGA connector or the DVI port or the HDMI port.

Serial buses

[edit]

Many communication systems were generally designed to connect two integrated circuits on the same printed circuit board, connected by signal traces on that board (rather than external cables).

Integrated circuits are more expensive when they have more pins. To reduce the number of pins in a package, many ICs use a serial bus to transfer data when speed is not important. Some examples of such low-cost lower-speed serial buses include RS-232, DALI, SPI, CAN bus, I²C, UNI/O, and 1-Wire. Higher-speed serial buses include USB, SATA and PCI Express.

Serial versus parallel

[edit]The communication links, across which computers (or parts of computers) talk to one another, may be either serial or parallel. A parallel link transmits several streams of data simultaneously along multiple channels (e.g., wires, printed circuit tracks, or optical fibers); whereas, a serial link transmits only a single stream of data. The rationale for parallel communication was the added benefit of having Direct Memory Access to the 8-bit or 16-bit registry addresses at a time where mapping direct data lanes was more convenient and faster than synchronizing data serially.[citation needed]

Although a serial link may seem inferior to a parallel one, since it can transmit less data per clock cycle, it is often the case that serial links can be clocked considerably faster than parallel links in order to achieve a higher data rate. Several factors allow serial to be clocked at a higher rate:

- Clock skew between different channels is not an issue (for unclocked asynchronous serial communication links). This can be caused by mismatched wire or conductor lengths.[17][18]

- A serial connection requires fewer interconnecting cables (e.g., wires/fibers) and hence occupies less space. The extra space allows for better isolation of the channel from its surroundings.

- Crosstalk is less of an issue, because there are fewer conductors in proximity.[17]

- Budgets for power use, power dissipation, cable cost, component cost, IC die area, PC board area, ESD protection, etc. can be focused on a single link.

The transition from parallel to serial buses was allowed by Moore's law which allowed for the incorporation of SerDes in integrated circuits.[19] An electrical serial link only requires a pair of wires, whereas a parallel link requires several. Thus serial links can save on costs (also known as the Bill of Materials). Differential signalling uses length-matched wires or conductors and are used in high speed serial links.[20] Length-matching is easier to perform on serial links as they require fewer conductors.

In many cases, serial is cheaper to implement than parallel. Many ICs have serial interfaces, as opposed to parallel ones, so that they have fewer pins and are therefore less expensive.

Examples of architectures

[edit]- ARINC 818 Avionics Digital Video Bus

- Atari SIO (Joe Decuir credits his work on Atari SIO as the basis of USB)

- Binary Synchronous Communications BSC - Binary Synchronous Communications

- CAN Control Area Network Vehicle Bus

- ccTalk Used in the money transaction and point-of-sale industry

- CoaXPress industrial camera protocol over Coax

- DMX512 control of theatrical lighting

- Ethernet

- Fibre Channel (high-speed, for connecting computers to mass storage devices)

- FireWire

- HDMI

- HyperTransport

- InfiniBand (very high speed, broadly comparable in scope to PCI)

- I²C multidrop serial bus

- MIDI control of electronic musical instruments

- MIL-STD-1553A/B

- Morse code telegraphy

- PCI Express

- Profibus

- RS-232 (low-speed, implemented by serial ports)

- RS-422 multidrop serial bus

- RS-423

- RS-485 multidrop multimaster serial bus

- SDI-12 industrial sensor protocol

- SERCOM

- Serial ATA

- Serial Attached SCSI

- Shift Register with serial-in and serial-out configuration

- SONET and SDH (high speed telecommunication over optical fibers)

- SpaceWire Spacecraft communication network

- SPI

- T-1, E-1 and variants (high speed telecommunication over copper pairs)

- Universal Serial Bus (for connecting peripherals to computers)

- UNI/O multidrop serial bus

- 1-Wire multidrop serial bus

See also

[edit]- 8N1

- Asynchronous serial communication

- Comparison of synchronous and asynchronous signalling

- Computer bus

- Data transmission

- Eye pattern

- Federal Standard 1037C

- High-Level Data Link Control (HDLC)

- List of device bandwidths

- MIL-STD-188

- Serial Peripheral Interface Bus

- Serial port

- Synchronous serial communication

- Universal asynchronous receiver/transmitter (UART)

References

[edit]- ^ Mackenzie, Charles E. (1980). Coded Character Sets, History and Development (PDF). The Systems Programming Series (1 ed.). Addison-Wesley Publishing Company, Inc. pp. 247–253. ISBN 978-0-201-14460-4. LCCN 77-90165. Archived (PDF) from the original on May 26, 2016. Retrieved December 29, 2022.

- ^ Robinson, Dan (12 January 2022). "Final PCIe 6.0 specs unleashed: 64 GTps link speed incoming... with products to follow in 2023". The Register.

- ^ "PCIe 7.0 Draft 0.5 Spec Available: 512 GB/S over PCIe x16 on Track for 2025".

- ^ "PCIe 5.0 is just beginning to come to new PCS, but version 6.0 is already here". 12 January 2022.

- ^ Handbook of Serial Communications Interfaces: A Comprehensive Compendium of Serial Digital Input/Output (I/O) Standards. Newnes. 21 August 2015. ISBN 978-0-12-800671-9.

- ^ "PAM4: For Better and Worse | 2019-02-26 | Signal Integrity Journal".

- ^ "PAM-4 Signaling".

- ^ Zhang, Hongtao; Jiao, Brandon; Liao, Yu; Zhang, Geoff. PAM4 Signaling for 56G Serial Link Applications − A Tutorial (PDF). DesignCon 2016.

- ^ "PAM4 Signaling in High-Speed Serial Technology: Test, Analysis, and Debug" (PDF) (application note). Tektronix.

- ^ Pan, Zhongqi; Yue, Yang (3 December 2019). Advanced DSP Techniques for High-Capacity and Energy-Efficient Optical Fiber Communications. ISBN 978-3-03921-792-2.

- ^ Essentials of Modern Communications. John Wiley & Sons. 4 August 2020. ISBN 978-1-119-52149-5.

- ^ Kim, Gain (January 2022). "Design Space Exploration of Single-Lane OFDM-Based Serial Links for High-Speed Wireline Communications". IEEE Open Journal of Circuits and Systems. 3 (1). Figure 2. doi:10.1109/OJCAS.2022.3189550. ISSN 2644-1225.

- ^ "Eye diagrams: The tool for serial data analysis". 4 June 2019.

- ^ "Advantages of PAM4 modulation | Disadvantages PAM4 signaling".

- ^ "Generate PAM4 signals for receiver compliance testing". 20 September 2016.

- ^ Complex Digital Hardware Design. CRC Press. 9 May 2024. ISBN 978-1-040-01179-9.

- ^ a b "Lecture 24" (PDF). CSE378: Machine Organization & Assembly Language.

- ^ Ledin, Jim; Farley, Dave (4 May 2022). Modern Computer Architecture and Organization: Learn x86, ARM, and RISC-V architectures and the design of smartphones, PCS, and cloud servers. Packt Publishing. ISBN 978-1-80323-823-4.

- ^ The Boundary — Scan Handbook. Springer. 30 June 2003. ISBN 978-1-4020-7496-7.

- ^ Ledin, Jim; Farley, Dave (4 May 2022). Modern Computer Architecture and Organization: Learn x86, ARM, and RISC-V architectures and the design of smartphones, PCS, and cloud servers. Packt Publishing. ISBN 978-1-80323-823-4.

External links

[edit]- Serial Interface Tutorial for Robotics (contains many practical examples)

- Serial interfaces listing (with pinouts)

- Wiki: Serial Ports

- Visual studio 2008 coding for Serial communication

- Introduction to I²C and SPI protocols Archived 2016-03-08 at the Wayback Machine

- Serial communication introduction

- Serial Port Programming in Linux Archived 2018-07-02 at the Wayback Machine