Zero-capacitor random-access memory

Zero-capacitor random-access memory, afkorting Z-RAM, is een nieuw soort computergeheugen dat ontwikkeld wordt door Innovative Sillicon (ISi)[1] Z-RAM gebruikt slechts 1 enkele transistor in tegenstelling tot SRAM (8, 6 of 4 transistors) en DRAM (1 transistor en 1 condensator). Hiermee elimineert men het probleem van de moeilijk te creëren condensator die zich bevindt in conventioneel DRAM-geheugen. Doordat de condensator wegvalt kan er op eenzelfde ruimte meer geheugen geplaatst worden en verbruikt het geheugen minder. Wat als gevolg heeft dat het goedkoper wordt om een bepaalde hoeveelheid aan geheugen te produceren.

Inleiding

[bewerken | brontekst bewerken]Door de toenemende vraag om zo veel mogelijk geheugen te kunnen plaatsen op een bepaalde ruimte probeerde men nieuwe technologieën te ontwikkelen die afstappen van de traditionele DRAM- en SRAM-ontwerpen. Z-RAM is er zo een van en maakt gebruik van een ontwerp met slechts één enkele transistor. Er zijn momenteel wel meerdere technologieën in ontwikkeling die gebruikmaken van een enkele transistor, maar Z-RAM lijkt het snelst furore te maken.

Doelstellingen

[bewerken | brontekst bewerken]De doelstellingen die Innovative Sillicon Inc. met Z-RAM voor ogen heeft zijn deze:

- Het dichtst op elkaar gepakte geheugen ter wereld.

- Goedkoopste geheugen ter wereld om te produceren.

- Productie aan de hand van huidige apparatuur, geen exotische processen.

- Dankzij het voordeel van de hogere densiteit, de kosten van Silicon On Insulator (SOI) verlagen.

Technologie

[bewerken | brontekst bewerken]Floating body effect

[bewerken | brontekst bewerken]Z-RAM exploiteert een elektrische eigenschap die eigen is aan het SOI-proces. Transistors die gemaakt worden op basis van SOI bezitten een extra virtuele parasitaire condensator, deze eigenschap wordt het Floating body effect[2] (FBE) genoemd. Het FBE wordt door velen als een nadeel beschouwd, maar net op deze virtuele condensator rust het hele principe van dit type geheugen. In 1990 werd een manier gevonden hoe men een bit kon opslaan bij 1 transistor (een geheugencel). Dit kon men enkel bij 1 geïsoleerde transistor, bij een geheugenmatrix corrumpeerde men altijd de naburige geheugencellen bij het schrijven. Pas in 2001 ontdekte men hoe men aan de hand van het FBE bits kon opslaan in een geheugenmatrix.

Werking

[bewerken | brontekst bewerken]Lezen

[bewerken | brontekst bewerken]Het lezen van Z-RAM geheugencel van de 1e generatie verloopt analoog met het lezen van een DRAM cel. De chip stuurt een kleine puls naar de transistor. Vervolgens meet een sense amplifier de stroom die door de transistor vloeit en vergelijkt deze met een referentiecel. Hierdoor weet men of er een '1' of een '0' opgeslagen is op de transistor. Bij Z-RAM van de 2e generatie heeft men deze referentiecel niet nodig. De reden hiervoor is dat de output eerder op een digitaal signaal lijkt en er zo een duidelijk verschil is tussen een '0' en een '1' dat men dus geen nood meer heeft aan referentiecellen.

Schrijven

[bewerken | brontekst bewerken]Het schrijven gebeurt gedeeltelijk anders dan bij traditioneel DRAM geheugen. In plaats van een lading op te slaan in een condensator en deze te meten vindt alles plaats in de transistor en wordt de stroom uitgemeten. Om een binaire '1' te schrijven wordt de transistor in saturatie gedreven. Als resultaat worden de elektronen die zich bevinden in de transistor tussen de source en de drain versneld. Hierdoor botsen ze tegen de siliciumatomen in de transistor wat op hun beurt zorgt dat er positieve gaten ontstaan. Deze positieve gaten nemen toe in aantal, wat als gevolg heeft dat er een positieve lading ontstaat binnen de transistor. Deze positieve lading, en de mogelijkheid om de stroom goed te geleiden, wordt beschouwd als een binaire '1'. Bij ISi spreekt men van impact ionization.

Om een '0' te schrijven zorgt men ervoor dat de transistor zich in Cutt-off bevindt. Hierdoor worden de positieve gaten weggevoerd via de source en bekomt men dus een sterk negatieve lading in de transistor. Deze negatieve lading, en de mogelijkheid om de stroom slecht te geleiden, wordt als een binaire '0' beschouwd. Bij ISi spreekt men hierbij van hole removal.

Schaling

[bewerken | brontekst bewerken]Voor een nieuwe technologie is het natuurlijk ook belangrijk dat deze goed schaalt. Dit wil zeggen dat men het ontwerp makkelijk naar een kleiner productieproces kan converteren. Bij DRAM is dit niet altijd zo makkelijk omdat er een condensator aanwezig is. Men kan deze niet te klein maken of men verliest de lading die men over de condensator plaatst. Een bijkomend nadeel van deze condensator is dat deze langwerpig van vorm is, wat niet al te bevorderlijk is om naar een kleiner proces te migreren. SRAM is ook niet zo ideaal om op een kleiner proces te produceren wegens toenemende lekkage en gevoeligheid aan Soft Error[:en:Soft_error.] Z-RAM daarentegen heeft deze nadelen niet omdat men niet met een condensator werkt. Hoe kleiner het proces wordt bij Z-ram, hoe meer voordeel je er eigenlijk uithaalt. De reden hiervoor is dat de lading die kan opgeslagen worden in de transistor steeds kleiner wordt, maar dat deze lading de stroom in de transistor sterker beïnvloedt. Aangezien bij het lezen van een Z-ram cel de stroom gemeten wordt is dit dus enkel maar voordelig. Dit wil natuurlijk niet zeggen dat het eenvoudig is om Z-RAM op een kleiner proces te fabriceren.

In praktijk bevinden Z-RAM, SRAM en DRAM zich dicht bij elkaar qua productieproces. Het modernste productieproces voor DRAM maakt tegenwoordig gebruik van 60 nm technologie, met 56 nm en kleiner in het vooruitzicht. SRAM wordt op allerlei technologieën geproduceerd, waaronder 90 nm,65 nm en 45 nm. Z-ram daarentegen wordt reeds geproduceerd aan de hand van een 90 nm en 65 nm proces, terwijl het gebruik van het 45 nm proces niet veraf is.

Evolutie

[bewerken | brontekst bewerken]

Na de introductie van de eerste generatie Z-RAM in 2004 zijn er tal van verbeteringen doorgevoerd. Deze verbeteringen aan het originele ontwerp leidden in 2006 tot de introductie van de 2e generatie Z-RAM. De veranderingen bij Gen2 (waarmee men duidt op de 2e generatie) zijn vooral terug te vinden in de geheugencel zelf. Er wordt bij Gen2 nog steeds gebruikgemaakt van dezelfde transistor als Gen1, maar er wordt gebruikgemaakt van een andere operatiemodus. Gen2 was een enorme stap voorwaarts ten opzichte van Gen1. Bij Gen1 maakte men gebruik van referentiecellen omdat het verschil tussen een binaire '1' en '0' behoorlijk klein was. Aan de hand van deze referentiecellen werd het dan duidelijk welke stroom de transistor doorliet. Gen2 zorgt op dit vlak voor een drastische verandering, aangezien er veel meer lading kan opgeslagen worden in de transistor. Hierdoor is het verschil tussen de stroomwaarden van een '1' en '0' zo groot dat er bijna sprake is van een puur digitaal signaal. Om deze reden heeft men dus geen nood meer aan referentiecellen. Ook kunnen de cellen nu tot 10 maal langer hun toestand behouden voor ze de binaire waarde die ze vertegenwoordigen verliezen. Dit heeft als grote voordeel dat men het aantal verversingscycli van het geheugen kan terugbrengen. Hierdoor verbruikt het geheugen op zijn beurt weer minder energie omdat men minder snel het geheugen moet herschrijven met de juiste waarden. Ook de hoeveelheid energie om het geheugen te beschrijven is gedaald met een factor 10, terwijl de energie die nodig is om het geheugen te lezen teruggedrongen is met een factor 4. Wat ook nieuw is aan Gen2 is dat men het geheugen voor verschillende doeleinden kan optimaliseren. Zo kan men geheugen maken dat zeer snel is maar iets meer verbruikt en meer plaats inneemt. Wanneer men geheugen wil dat zo weinig mogelijk verbruikt, zal echt de snelheid dalen maar zal het minder plaats innemen en zuiniger zijn. Hieronder zijn alle verbeteringen samengevat in een tabel.

| Gen1 | Gen2 | |

|---|---|---|

| Maximale frequentie | 200 MHz | 400 MHz |

| Verbruik tijdens lezen | 1.0 (referentie) | ~0.25X |

| Verbruik tijdens Schrijven | 1.0 (referentie) | ~0.10X |

| Retentie tijd | 1.0 (referentie) | ~10X |

| Densiteit bij 45 nm proces | ~10Mbit per mm² | ~10Mbit per mm² |

Z-RAM lay-out

[bewerken | brontekst bewerken]Op zichzelf zijn geheugencellen compleet nutteloos, daarom is er een hele infrastructuur rondgebouwd om informatie in en uit de cellen te krijgen. De lay-out van Z-RAM geheugen verschilt in principe niet zo veel van de standaard DRAM geheugenchip lay-out. Het enige verschil is dat de lay-out van Z-RAM bestaat uit enkel rechte lijnen. Er wordt dus ook gebruikgemaakt van Bit lines,Word Lines, Source Lines en sense amplifiers. Buiten deze componenten wordt er nog gebruikgemaakt van row driver en spanningomzetters. De Row driver zorgt ervoor dat de Word line steeds de juiste spanning toebedeeld krijgt zodat de operaties (Write, Read, Hold) juist worden uitgevoerd. De spanningomzetters hun taak bestaat eruit de chip te voorzien van alle nodige spanningen.

- Cell lay-out bij Z-RAM

- Z-RAM cell lay-out van bovenaf, wat de rode lijn omcirkelt vertegenwoordigt 1 Z-RAM cel.

- Doorsnede van Z-RAM cell, wat de rode lijn omcirkelt vertegenwoordigt 1 Z-RAM cel.

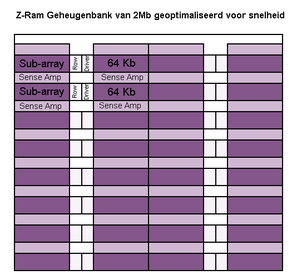

Een gebruikelijke Z-RAM geheugenbank heeft een grootte van 4Megabit, die bestaat uit 8 blokken van 512Kb geheugencellen bestaande uit 4 rijen en 2 kolommen. Deze geheugenblok van 512kb wordt ook wel een sub-array genoemd. Tussen elk van deze sub-arrays bevinden zich de sense amplifiers. De Row drivers bevinden zich tussen de 2 kolommen van sub-arrays. Als men Z-ram wil optimaliseren voor snelheid maakt men gebruik van 'sub-arrays' met een grootte van 64kb. Hierdoor neemt een geheugenbank wel meer ruimte in en daalt de densiteit van het geheugen.

- Normale geheugenbank van 4Mbit

- Geheugenbank geoptimaliseerd voor snelheid (2Mbit).

Vergelijking met andere types geheugen

[bewerken | brontekst bewerken]Hieronder bevindt zich een tabel die alle verschillen opsomt tussen Z-RAM, DRAM en SRAM.

| Z-Ram | DRAM | SRAM | |

|---|---|---|---|

| Ontwerp | 1 Transistor | 1 Transistor + 1 Condensator | 4, 6 of 8 Transistors |

| Densiteit | 1x (referentie) | 2x | 5x |

| Snelheid | Snel | Middelmatig | Zeer snel |

| Soft Error | Ongevoelig | Ongevoelig | Gevoelig |

| Productieproces | Standaard SOI | Bulk CMOS met extra stappen | Bulk CMOS |

| Energieverbruik | Laag | Redelijk laag tot middelmatig | Hoog |

| Retentie tijd | Middelmatig | Laag | Heel Hoog |

Mogelijke toepassingen

[bewerken | brontekst bewerken]Z-RAM lijkt vooral handig voor geheugenfabrikanten omdat de dichtheid 2 keer zo groot is in vergelijking met conventioneel DRAM. Maar omdat het gebruikmaakt van SOI zouden deze fabrikanten hun hele fabriek met andere machines moeten uitrusten. Z-RAM is momenteel voor deze fabrikanten dus ook niet echt nuttig. De fabrikant Hynix[3] heeft echter toch een licentie genomen op de Z-RAM technologie. Waar Z-RAM wel bij gebruikt kan worden is bij SoC (system on chip) systemen, bij draagbare apparaten als embedded geheugen en als cache geheugen in CPU’s. De meest voor de hand liggende markt is die van onder andere GSM’s, draagbare telefoons en PDA’s. Deze apparaten hebben geheugen nodig dat niet veel verbruikt en niet veel plaats inneemt. Een andere markt die in het vooruitzicht ligt is die van de CPU’s. Advanced Micro Devices[4] heeft reeds een licentie op Z-RAM en maakt voor zijn processors gebruik van SOI. Om de L1 en L2 cache van de CPU te vervangen is Z-RAM niet snel genoeg. Maar de recentste processors van AMD maken gebruik van een tragere L3 cache. Hiervoor is Z-RAM wel voldoende snel en zou het in de toekomst misschien kunnen worden gebruikt.

- (en) Innovative Silicon Inc., [1], Microprocessor Report independent analysis of Z-RAM.

- (en) IEEE Spectrum, Masters of Memory, door Samuel K. Moore, januari 2007.

- (en) EETimes, AMD neemt een licentie op Z-RAM.

- (en) EETimes, Hynix neemt een licentie op Z-RAM.