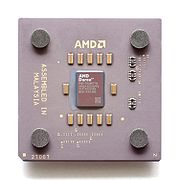

AMD Duron

Van Wikipedia, de gratis encyclopedie

Van Wikipedia, de gratis encyclopedie

| AMD Duron >> | |

|---|---|

| |

| Produktion: | 2000 bis 2004 |

| Produzent: | AMD |

| Prozessortakt: | 600 MHz bis 1,8 GHz |

| FSB-Takt: | 100 MHz bis 133 MHz |

| L2-Cachegröße: | 64 KiB |

| Befehlssatz: | x86 |

| Mikroarchitektur: | AMD K7 |

| Sockel: | Sockel A |

Namen der Prozessorkerne:

| |

AMD Duron ist der Markenname einer Reihe preisgünstiger Mikroprozessormodelle der Firma Advanced Micro Devices, die im Zeitraum 2000 bis 2004 produziert wurden. Sie basieren wie die im selben Zeitraum angebotenen Athlon-Prozessoren auf der Mikroarchitektur AMD K7. Während Athlon-Modelle auch für den so genannten Slot A produziert wurden, kamen Duron-Modelle nur als CPGA für den Sockel A auf den Markt. Der Name Duron (abgeleitet von lateinisch durus, deutsch hart, ausdauernd) sollte auf die Dauerhaftigkeit des Produktes hinweisen. Die Prozessorreihe wurde in Konkurrenz zu den Celeron-Modellen der Firma Intel vermarktet.

Produktgeschichte

[Bearbeiten | Quelltext bearbeiten]Die ersten Durons mit den Entwicklungsnamen Spitfire und Morgan wurden in 0,18-µm-Technik gefertigt und stammten direkt vom Athlon Thunderbird bzw. Athlon XP Palomino ab, unterschieden sich aber durch die Verkleinerung des L2-Cache auf nur 64 KiB von diesen (was geringere Herstellungskosten zur Folge hatte). Diese erste Reihe war für Takte bis 950 (Spitfire) bzw. 1.300 MHz (Morgan) erhältlich, immer gepaart mit einem FSB von 100 MHz.

Die späteren Modelle namens Applebred wurden in 0,13 µm gefertigt und waren mit 133 MHz FSB und Taktfrequenzen bis 1.800 MHz erhältlich. Die technische Basis war hier der Athlon XP Thoroughbred A/B mit physisch vorhandenen 256 KiB L2-Cache, der aber bis auf 64 KiB deaktiviert wurde; auf diese Weise konnten auch für die Athlon-Produktlinie hergestellte Chips verkauft werden, die Fehler im Bereich des L2-Cache aufwiesen, so dass nicht die vollen 256 KiB nutzbar waren. Gemeinsam ist allen Durons die L1-Cache-Größe von 2 × 64 KiB und die L2-Cache-Größe von 64 KiB on-Die, während die Sockel-A-Athlons generell mit L2-Caches von 256 oder 512 KiB (letzte Ausführung des Athlon XP mit Codenamen Barton) ausgestattet waren.

Einige Exemplare (Baureihen) des Duron ließen sich durch schrittweise Erhöhung des FSB und einfache Veränderung des Multiplikators ziemlich weit übertakten. Außerdem war es bei einigen Baureihen möglich, sie mit minimalen Modifikationen im Multiprozessorbetrieb zu nutzen.

Trotz seines durchaus vorhandenen Erfolgs schien der Duron oft eine Art AMD-Stiefkind zu sein. Nach dem 1300-MHz-Modell dauerte es recht lange, ehe Varianten mit 1400, 1600 und 1800 MHz erschienen; außerdem wurde das Low-End-Modell nie mit einem Performance-Rating entsprechend dem des Athlon XP versehen. Das hatte zur Folge, dass der Duron gegen Intels Celeron-CPUs mit mehr als 2 GHz marketingtechnisch einen schweren Stand hatte (obwohl er diesem hinsichtlich Preis und Leistung keineswegs unterlegen war). Der somit eher bescheidene Ruf des Duron führte letztendlich dazu, dass AMD (wohl auch auf Druck großer Hersteller wie Lenovo und Asus) die Modellreihe 2004 vollständig einstellte und begann, das untere Leistungssegment mit den neuen Sempron-Prozessoren zu bevölkern, die technisch vollwertige Athlon XP mit vergleichsweise geringen Taktraten (ab 1500 MHz) waren.

Modelldaten

[Bearbeiten | Quelltext bearbeiten]Spitfire

[Bearbeiten | Quelltext bearbeiten]

- L1-Cache: 64 + 64 KiB (Daten + Instruktionen)

- L2-Cache: 64 KiB mit Prozessortakt

- MMX, Extended 3DNow!

- Sockel A, EV6 mit 100 MHz Front Side Bus (FSB 200)

- Betriebsspannung (VCore): 1,50–1,60 V

- Erstes Erscheinungsdatum: 19. Juni 2000

- Fertigungstechnik: 0,18 µm

- Die-Größe: 100,0 mm² bei 25,0 Millionen Transistoren

- Taktraten: 600–950 MHz

- 600 MHz [19. Juni 2000]

- 650 MHz [19. Juni 2000]

- 700 MHz [19. Juni 2000]

- 750 MHz [5. September 2000]

- 800 MHz [17. Oktober 2000]

- 850 MHz [8. Januar 2001]

- 900 MHz [2. April 2001]

- 950 MHz [6. Juni 2001]

Morgan

[Bearbeiten | Quelltext bearbeiten]

- L1-Cache: 64 + 64 KiB (Daten + Instruktionen)

- L2-Cache: 64 KiB mit Prozessortakt

- MMX, Extended 3DNow!, SSE

- Sockel A, EV6 mit 100 MHz Front Side Bus (FSB 200)

- Betriebsspannung (VCore): 1,75 V

- Erstes Erscheinungsdatum: 20. August 2001

- Fertigungstechnik: 0,18 µm

- Taktraten: 0,9–1,3 GHz

- Die-Größe: 105,68 mm² bei 25,2 Millionen Transistoren

- 1,0 GHz [20. August 2001]

- 1,1 GHz [1. Oktober 2001]

- 1,2 GHz [15. November 2001]

- 1,3 GHz [21. Januar 2002]

Applebred

[Bearbeiten | Quelltext bearbeiten]

Der Applebred-Kern gleicht einem Thoroughbred-A/-B-Kern des Athlon XP, bei dem Teile des L2-Caches deaktiviert sind.

- L1-Cache: 64 + 64 KiB (Daten + Instruktionen)

- L2-Cache: 64 KiB mit Prozessortakt

- MMX, Extended 3DNow!, SSE

- Sockel A, EV6 mit 133 MHz Front Side Bus (FSB 266)

- Betriebsspannung (VCore): 1,50 V

- Erstes Erscheinungsdatum: 21. August 2003

- Fertigungstechnik: 0,13 µm

- Die-Größe: 80,89 mm², 84,66 mm² bzw. 86,97 mm² bei 37,2 Millionen Transistoren

- Taktraten: 1,4–1,8 GHz

- 1,4 GHz [21. August 2003]

- 1,6 GHz [21. August 2003]

- 1,8 GHz [21. August 2003]