ディプリーション負荷NMOSロジック

ディプリーション負荷NMOSロジック(ディプリーションふかNMOSロジック、Depletion-load NMOS logic)は、集積回路におけるロジック・ファミリの一形式である。それは初期のNMOSロジックファミリーが2つ以上の異なる電源電圧を必要としたのと違って単一電源電圧だけを使用する[注釈 1]。 この集積回路を製造するために追加の製造工程を必要としたが、スイッチング速度が向上したことと外部電源の種類を減らしたことによって、このロジックファミリは多くのマイクロプロセッサとその他の論理回路に対して好ましい選択肢となった。インテルはこの技術をHMOSと称していた[1]。

負荷トランジスタとしてディプリーションモードn型MOSFETを使うことによって、単一電源動作が可能となり、エンハンスメントモードMOSFETを負荷トランジスタとして使った以前のNMOSよりも高速になった。 ディプリーションモードMOSFETは、より単純なエンハンスメントモードMOSFETよりも電流源に近い動作をすることが性能向上の理由の一部である。特に複数の電圧が使えないときにディプリーションモードMOSFETの方が速度的により有利になる(初期のPMOSとNMOSチップが複数の電圧を要求した理由の一つである)[2]。

製造過程にディプリーションモードNMOSトランジスタを入れることは、より単純なエンハンスメントモード負荷の回路と比べて追加の工程を必要とする。 ディプリーションデバイスは、閾値電圧を変更するために負荷トランジスタのチャネル領域におけるドーパントの量を増やすことによって作られる。 その工程は、通常イオン注入を使って行われる。

1980年代の間にCMOSは、ほとんどのNMOS設計のチップを置き換えたが、いくつかのディプリーション負荷NMOS設計のチップは未だに製造されている。大抵、新しくCMOSに再設計されたものと並行して製造されている。 NMOSのZ84015[3]とCMOSのZ84C15[4]がその一例である。

歴史と背景

[編集]ベル研究所のモハメド・アタラとダウォン・カーンによるMOSFETの発明に続いて、彼らは1960年にMOSFET技術を発表した[5]。 彼らは20μmプロセスでPMOSとNMOSの両方を製造した。 しかしながらNMOSデバイスは実用性がなかった。PMOSデバイスだけに実用性があった[6]。

1965年にフェアチャイルドセミコンダクターのチータン・サー、オットー・レイスティコ(Otto Leistiko)、そしてA・S・グローブ(A.S. Grove)は、チャネル長が10μmから65μmの間でいくつかのNMOSデバイスを製造した[7]。 IBMのデイル・L・クリッチロー(Dale L. Critchlow)とロバート・H・デナードも1960年代にNMOSデバイスを製造した。 最初のIBMのNMOS製品は、1Kbitのデータ容量かつ50/100nsのアクセス時間のメモリチップであった。そのメモリチップは、1970年代初頭に大量生産に入った。 これによってMOSFETの半導体メモリが1970年代のバイポーラメモリと磁気コアメモリの技術を置き換えることになった[8]。

シリコンゲート

[編集]1960年代後半にバイポーラトランジスタは、(p型チャネル)MOSFETよりも高速だったので、よく利用され、信頼性も高かった。しかし、バイポーラトランジスタは、より多くの電力を消費し、広い面積を必要とし、より複雑な製造工程を必要とした。 MOSFETの集積回路は、興味深いと考えられていたが、高速なバイポーラトランジスタに取って代わるには速度が不十分であったので、低消費電力用途のようなニッチ市場向けであった。 MOSFETの低速度の理由の一つは、MOSFETがアルミニウムで作られたゲート電極を持つことであった。アルミニウムのゲート電極は、当時の製造工程を使うとかなりの寄生容量をもたらすことになった。 ポリシリコンゲート(1970年代中期から2000年代初頭まで事実上の標準であった)の導入は、このハンディキャップを減らすための重要な最初の一歩であった。 この新しい自己整合シリコンゲートMOSFETは、1968年初め頃にフェアチャイルドセミコンダクターのフェデリコ・ファジンによって導入された。 自己整合シリコンゲートは、ジョン・C・サラス(John C. Sarace)、トム・クレイン(Tom Klein)そしてロバート・W・バウアーによるさらに低い寄生容量を実現するためのアイデアと仕事の改良(そして最初に動作する実装)であった。その改良は、ディスクリート部品としてだけでなくIC(集積回路)の一部として製造することができた。 この新型のMOSFETは、1ワット当たりでアルミニウムゲートのpMOSトランジスタの3倍から5倍高速であった。さらに面積も小さくなり、より少ない漏れ電流とより高い信頼性を持っていた。 同年、ファジンは新型MOSFETを使った最初のICも作った。フェアチャイルド3708(8ビットバイナリデコーダー付きのアナログマルチプレクサ)である。これは金属ゲートの同型のものより大幅に性能が向上したことを証明した。 それから10年以内にシリコンゲートMOSFETは、複雑なデジタルICのための主な媒体としてバイポーラトランジスタを置き換えた。

NMOSとバックゲートバイアス

[編集]PMOS(p型MOSFET)に関連する欠点が2つある。PMOSトランジスタの電荷キャリアである正孔は、NMOSトランジスタの電荷キャリアである電子よりも移動度が低い(正孔の移動速度は電子よりも約2.5倍ほど遅い)。さらにPMOS回路は、Diode-transistor logic(DTL)やTransistor-transistor logic(TTL)(7400シリーズ)のような低電圧かつ正電圧の論理回路と容易に相互接続できない(入出力信号が負電圧のため)。 しかしながら、PMOSトランジスタは比較的容易に作ることができ、それゆえに最初に開発された。エッチングとその他の要因によるゲート酸化膜のイオン汚染は、電子に基づいたNMOSトランジスタのスイッチングオフを非常に容易に妨げることになる。一方で正孔に基づいたPMOSトランジスタは、それほど影響を受けない。 それゆえにNMOSトランジスタの製造は、実際に動作するデバイスを製造するためにバイポーラトランジスタの工程よりも多くの回数の洗浄を必要とする。

NMOS集積回路(IC)の技術における初期の業績は、1969年の国際固体回路会議(ISSCC)におけるIBMの短い論文で発表されている。 それからヒューレット・パッカード(HP)は、電卓の速度と容易な操作性を保証するためにNMOS IC技術の開発を始めた[注釈 2]。 HPのトム・ハスウェルは、より純度の高い物質(特に接続に使うアルミニウム)を使用し、ゲートスレッシュホールド電圧を十分に大きくするためにバイアス電圧を追加することによってついに多くの問題を解決した。 このバックゲートバイアスは、イオン注入(以下参照)が開発されるまでゲート内の主な汚染であるナトリウム汚染を解決する事実上の標準的方法として存続した。 1970年までにHPはすでに十分良いNMOS ICを作成しており、十分に差別化できていたので、デイブ・メイトランド(Dave Maitland)は、1970年12月発行のエレクトロニクスマガジンにNMOSについての記事を書くことができた。 しかしながら、NMOSは1973年までHP以外の半導体産業において非一般的なものであった[注釈 3]。

量産可能なNMOSプロセスによって、HPは半導体産業の最初の4Kbit ROMを開発できた。 モトローラは、ついにHP製品のセカンドソースとして働くことになり、NMOSプロセスを習得するために最初の商業半導体供給業者の一つになった。ヒューレット・パッカードのおかげであった。 しばらくしてからスタートアップ企業インテルは、1102と呼ばれる1Kbit PMOS DRAMを発表した。1102はハネウェルのための特注品として開発された(ハネウェルのメインフレームの磁気コアメモリを置き換えようとした)。 HPの電卓の技術者は、似たようなものを欲したが、HP 9800シリーズのためにより堅牢な製品を求めた。HPは、インテルのDRAMの信頼性、動作電圧、そして動作温度範囲を改善するためにHPの4Kbit ROMの製造経験を提供した。 これらの努力は、大幅に進歩したIntel 1103 1Kbit PMOS DRAMに貢献した。1103は世界初の商業的に入手可能なDRAM ICであった。 1103は、1970年10月に正式に発表され、インテルの本当に成功した最初の製品になった[9]。

ディプリーションモードMOSFET

[編集]

ディプリーション負荷NMOSロジックにおいてVGS = 0Vの曲線だけを使う。ディプリーションモードなので、VGS ≦ 0で使用する必要がある。

初期のMOSFETロジックは、一つのMOSFETで構成されており、エンハンスメントモードだったので、論理スイッチとして動作することができた。 適切な抵抗を作るのが難しいので、論理ゲートは飽和したMOSFETを負荷抵抗として使った。負荷抵抗として動作するMOSFETを作るためにMOSFETのゲート電極を電源(PMOSロジックの場合は負電源。NMOSロジックの場合は正電源)に接続することによって常にONさせる必要があった。 その方法で接続されたMOSFETの電流は、負荷に印加される電圧の2乗になる。そのため、プルアップ時(出力High)は負荷に印加される電圧が低くなり、電流があまり流れないので、プルアップに時間がかかる。一方、プルダウン時(出力Low)は負荷に印加される電圧が高くなり、電流が増えるので、プルダウンは短時間で終わる。 MOSFETを抵抗の代わりに使うよりも本当の抵抗(電流は電圧に単純に比例する)の方が良く、電流源(電圧に関係なく電流が一定)はさらに良い。 ソース電極とゲート電極を接続したディプリーションモードMOSFETは、エンハンスメントモードMOSFETよりもかなり良い負荷になる。抵抗と電流源の中間的な動作をするからである。

最初のディプリーション負荷NMOS回路は、DRAMメーカーのモステックによって開拓され製造された。モステックは、1975年から1976年までのオリジナルのザイログZ80の設計にディプリーションモードMOSFETを使えるようにした[注釈 4]。 モステックは、拡散法よりもドーピング特性を正確に制御するために必要なイオン注入の設備を有していたので、負荷MOSFETの閾値電圧を正確に調整できた。 インテルにおいてディプリーション負荷はフェデリコ・ファジンによって1974年に導入された。ファジンは元フェアチャイルドセミコンダクターの技術者であり、後にザイログを創業することになった。 ディプリーション負荷は、当時のインテルの最重要製品の一つを再設計するために最初に使用された。再設計されたのは2102と呼ばれる+5V単一電源の1Kbit NMOS SRAMであった(6000個以上のMOSFETを使用した[注釈 5])。 この再設計の結果は、格段に高速な2102Aとして結実した。2102Aは、2102の高性能版であり、アクセス時間は100ns未満であった。これによってMOSFETのメモリは最初にバイポーラRAMの速度に近づいた[10]。

ディプリーション負荷のプロセスは、有名な8ビットCPU、16ビットCPU、そして32ビットCPUを製造するためにいくつかの他の製造者によっても使われた。 負荷としてエンハンスメントモードMOSFETを使う初期のPMOSとNMOSのCPUの設計と同様に、ディプリーション負荷NMOSを使った設計は、動的ロジックあるいは動的なクロック同期ラッチ回路として使われるパストランジスタロジックの多くの種類に一般的に使用された。 これらの技術は、一概に高速化するとは言えないが、面積効率を大幅に改善することができる。 ディプリーション負荷NMOS回路で作られたプロセッサは、MC6800(後期版[11])、MOS 6502、Signetics 2650、Intel 8085、MC6809、Intel 8086、Z8000、NS32016、そして多くのその他のプロセッサが含まれる。

サポートICや周辺ICの多くも(しばしば静的な)ディプリーション負荷NMOSロジックを基本とした回路を使って実装された。 しかしながらバイポーラの7400シリーズ 汎用ロジックICやCMOSの4000シリーズ 汎用ロジックICのような標準化された汎用ロジックICは、NMOSに存在しなかった。 いくつかのセカンドソース製造者によるディプリーション負荷NMOSロジックの設計は、事実上の標準としての地位を達成することがよくあったにもかかわらずである。 その一例としてNMOSで設計された8255 PIOがある。元々は8085の周辺チップとして設計されたが、Z80とx86の組み込みシステム、そして数十もの多くの他の環境で使用されてきた。 7400シリーズと同様に8255 PIOの近代的な低消費電力版がCMOSあるいはBiCMOSで実装されて入手できた。

インテル HMOS

[編集]インテル独自のディプリーション負荷NMOSは、HMOS(High density, short channel MOS:高密度・短チャネルMOS)として知られていた。 最初のバージョンは1976年に導入され、インテルのSRAM製品に最初に使われた[12]。まもなく、8085、8086、そしてその他のチップの高速版あるいは低消費電力版に使われた。

HMOSは改良され続け、4つの明確な世代を通過した。 インテルによると、HMOS II(1979年)は、同世代の他の一般的なディプリーション負荷NMOSプロセスの2倍の密度かつ電力あたりで4倍の速度の製品を提供した[13]。 このバージョンは多くのサードパーティーとライセンス契約を交わすことになった。モトローラはMC68000のためにHMOS IIを使った。コモドール・セミコンダクター・グループはMOS 6502を微細化したMOS 8502のためにHMOS IIを使った。

最初のHMOSプロセス(後にHMOS Iとされる)は、チャネル長が3ミクロンだった。チャネル長は、HMOS IIで2ミクロン、HMOS IIIで1.5ミクロンであった。 HMOS IIIが導入された1982年までにインテルは、HMOSシリーズの設計要素を使ったCMOSプロセスであるCHMOSプロセスへ切り替えを始めた。 HMOSの最終バージョンであるHMOS-IVも発売された。 HMOSシリーズの重要な利点は、各世代のHMOSが既存のレイアウトを大きな変更をせずに微細化できるように意図的に設計されていたことであった。 レイアウトを変更してもシステムが動作することを保証するために多くの技術が導入された[14][15]。

HMOS、HMOS II、HMOS III、そしてHMOS IVは、多くの異なった種類のプロセッサに使用された。Intel 8085、Intel 8048、Intel 8051、Intel 8086、Intel 80186、Intel 80286そしてその他の多くのプロセッサだけでなく、同一の基本設計でHMOSのいくつかの世代にまたがったものについてはデータシートを参照すること。

さらなる発展

[編集]1980年代中期にインテルのCHMOS I, II, III, IVなどのHMOSプロセス技術を使ったより高速なCMOSの品種がIntel 80386や特定のマイクロコントローラに使われるようになり、nチャネルのHMOSを置き換え始めた。 数年後、1980年代後半、BiCMOSが高性能マイクロプロセッサだけでなく高速アナログ回路のために導入された。 現在、普及した7400シリーズを含むほとんどのデジタル回路は、採用された様々なトポロジーの範囲で各種CMOSプロセスを使って製造されている。

CMOSとの比較

[編集]静的CMOSと比較して、全種類のNMOS(とPMOS)は、定常状態において比較的電力を多く求める。 この原因は、抵抗器の代わりとして動作する負荷トランジスタに依存しているからである。ここで静止電流は、出力における最大負荷だけでなく論理ゲートの速度を決定する(他の要因が一定のとき)。 このことは静的CMOS回路の消費電力特性と比べて対照的である。CMOSは、出力状態が変化するときにだけ遷移電力を消費し、pチャネル型MOSFETとnチャネル型MOSFETは短時間だけ同時に導通するので、低消費電力である。

以前のNMOSロジックからの進化

[編集]ディプリーション負荷NMOSロジックは、従来のNMOSであるエンハンスメントモード負荷型よりも速度が速く、消費電力も少なくなっている。その理由について説明する。

標準的なNMOSロジックの問題

[編集] 閾値電圧 VTは0Vよりも少しだけ高い値のことが多い。エンハンスメントモードなので、VGS ≧ 0 で使用する。 |  |  |

集積回路内部に抵抗器を作ると工数が増える[18]。MOSFETを抵抗器の代わりに使うと工数を削減できる。それを負荷トランジスタや負荷MOSFETという[19]。そのため、nチャネルMOSFETだけで回路全体を作ることができる。しかし、負荷MOSFETの電気特性は抵抗器と異なる。

負荷トランジスタ(プルアップトランジスタ)は論理スイッチとして使われるものと同種のエンハンスメントモードMOSFETである(ゲート・ソース間電圧VGSが0になるとオフになる)[20]。

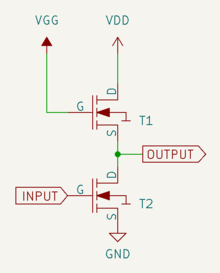

図のように負荷MOSFETのゲートをどこに接続するのかで負荷の種類が異なる。負荷MOSFETのゲートをVddに接続すると飽和エンハンスメント負荷となり、Vggに接続すると線形エンハンスメント負荷となる。線形エンハンスメント負荷の方が電圧降下が少ないため出力電圧をVddに近くできるが、2電源が必要になる[17]。

回路図から負荷MOSFETの動作を決める変数は以下のようになる。

- ドレイン・ソース間電圧 VDS = Vdd - 出力電圧

- ゲート・ソース間電圧 VGS = Vdd - 出力電圧(飽和エンハンスメント負荷のとき)

- ゲート・ソース間電圧 VGS = Vgg - 出力電圧(線形エンハンスメント負荷のとき)

- ドレイン・ソース間電流 IDS = VDS のおおよそ2乗に比例

出力電圧が低下すると、VDS と一緒に VGS も増えることになる。そのため、IDS は、VDS のおおよそ2乗に比例して増えることになる。つまり出力電圧が低下すると過剰な電流が流れて消費電力が悪化する。その一方で出力電圧が増大すると電流がわずかしか流れないので、動作速度が低下する。

このように抵抗器の代わりにエンハンスメントモードMOSFETを使う方法は速度や消費電力の面で問題がある[17][21]。

ディプリーション負荷NMOSロジックによる改良

[編集] ディプリーション負荷NMOSロジックにおいてVGS = 0Vの曲線だけを使う。ディプリーションモードなので、VGS ≦ 0で使用する必要がある。 |  |

ディプリーション負荷NMOSロジックは、負荷NMOSトランジスタだけをディプリーションモードMOSFETに置き換える[2]。

回路図から明らかなように負荷MOSFETの動作を決める変数は以下のようになる。

この負荷MOSFETは、ゲート端子をソース端子に直接接続しているので、常にVGS = 0V になる。ディプリーションモードなので、VGS が0Vでも電流を流すことができる。そのため、VDS だけでIDS が決まる。

出力が0のとき、VDS ≒ Vdd なので、MOSFETの飽和領域(Saturation region)を使うことになる。しかし、VGS = 0Vなので、IDS はほぼ一定になる(電流源に近い)。そのため、標準的なNMOSロジックよりも消費電力が少なくなる。出力が0から1へ遷移しているとき、出力電圧はVddに近づくので、VDS は小さくなり、MOSFETの線形領域(Linear region)を使うことになるので、IDS は VDS にほぼ比例する(抵抗器に近い)。そのため、負荷トランジスタは急激にオフにならず、IDSはそれなりに流れる。その結果、0から1への遷移が高速になる。

静的な消費電力

[編集]

ディプリーション負荷回路は、同一速度でエンハンスメントモード負荷回路よりも少ない電力を消費する。 どちらにしても入力を1に接続すると、負荷デバイスは常にONになる。この結果として大きな静的消費電力になる。 無駄な消費電力の量は、プルアップ負荷の流せる電流あるいは物理的大きさに依存する。 エンハンスメントモード負荷とディプリーションモード負荷はともに出力が0で安定した時により大きな電力を使う。この損失はかなり大きい。

前述のようにエンハンスメント負荷の場合、ドレイン・ソース間電流IDSは、ドレイン・ソース間電圧VDSのおおよそ2乗に比例して増えるので、負荷が完全にオンになっているときに大量の電流が流れてしまう。ディプリーション負荷の場合、VDSの値が高い時でもIDSは電流源のように一定になるので、エンハンスメント負荷よりは消費電力が少なくなる。

関連項目

[編集]注釈

[編集]- ^ 初期のNMOSで作られたIntel 8080は、TTLとの互換性のために3電源(+12V, +5V ,-5V)を必要とした。

- ^ これらの電卓(Datapoint 2200とその他のようなもの)は、色々な意味でデスクトップコンピュータであった。長年の間、Apple IIとIBM PCよりも先行していた。

- ^ "IEEE Transactions on Manufacturing Technology"1972年12月号に掲載され、GEの技術者であるハーマン・シュミット(Herman Schmid)によって書かれた長い総括記事における単なる言及によって示されている。それはElectronics誌のメイトランド(Maitland)の1970年の記事を引用しているが、シュミットの記事はNMOSの製造を詳細に述べていない。しかし、その記事はPMOSとCMOSの製造を幅広く網羅する。

- ^ ザイログは自社の製造設備が使えるようになるまでZ80やその他のチップの生産をMostekとSynertekに依存していた。

- ^ 一般的なSRAMにおいて1ビットに6個のトランジスタが必要である。

出典

[編集]- ^ 半導体プロセスまるわかり インテルから学ぶプロセスの歴史(2014年02月10日)

- ^ a b The Depletion Load (The University of Kansas)

- ^ See http://www.zilog.com/index.php?option=com_product&Itemid=26&mode=showProductDetails&familyId=20&productId=Z84015.

- ^ See http://www.zilog.com/index.php?option=com_product&Itemid=26&mode=showProductDetails&familyId=20&productId=Z84C15.

- ^ “1960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated”. The Silicon Engine (Computer History Museum).

- ^ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. pp. 321–3. ISBN 9783540342588

- ^ Sah, Chih-Tang; Leistiko, Otto; Grove, A. S. (May 1965). “Electron and hole mobilities in inversion layers on thermally oxidized silicon surfaces”. IEEE Transactions on Electron Devices 12 (5): 248–254. doi:10.1109/T-ED.1965.15489.

- ^ Critchlow, D. L. (2007). “Recollections on MOSFET Scaling”. IEEE Solid-State Circuits Society Newsletter 12 (1): 19–22. doi:10.1109/N-SSC.2007.4785536.

- ^ “Prologues”. Hp9825.com. 2022年3月15日閲覧。

- ^ See for instance: http://www.intel4004.com/sgate.htm or http://archive.computerhistory.org/resources/text/Oral_History/Faggin_Federico/Faggin_Federico_1_2_3.oral_history.2004.102658025.pdf Archived 2017-01-10 at the Wayback Machine.

- ^ “Motorola Redesigns 6800”. Microcomputer Digest (Santa Clara, CA: Microcomputer Associates) 3 (2): 4. (August 1976). "Motorola is redesigning the M6800 microprocessor family by adding depletion loads to increase speed and reduce the 6800 CPU size to 160 mils."

- ^ Volk, A.M.; Stoll, P.A.; Metrovich, P. (2001). “Recollections of Early Chip Development at Intel”. Intel Technology Journal 5 (Q1).

- ^ See for instance: Scanlon, Leo J.; Moody, C.W. (1981). The 68000 Principles and programming. H.W. Sams. ISBN 978-0-672-21853-8. OCLC 7802969

- ^ HMOS III Technology. ISSCC 82. 1982.

- ^ Atwood, G.E.; Dun, H.; Langston, J.; Hazani, E.; So, E.Y.; Sachdev, S.; Fuchs, K. (October 1982). “HMOS III technology”. IEEE Journal of Solid-State Circuits 17 (5): 810–5. doi:10.1109/JSSC.1982.1051823.

- ^ トランジスタの構造と基本特性 (2) 日本電気技術者協会

- ^ a b c d Inverters with different types of load (Madan Mohan Malaviya University of Technolog)

- ^ 半導体集積回路の概要と試作品の特性(日立評論)

- ^ How to use MOSFET as an active load resistor? (StackExchange)

- ^ MOSFET Circuits (Electrical4U)

- ^ Chapter 13 MOS Digital Circuits (McGill University)