磁気コアメモリ

ウィキペディアから無料の百科事典

ウィキペディアから無料の百科事典

磁気コアメモリ(じきコアメモリ)は、小さなドーナツ状のフェライトコアを磁化させることにより情報を記憶させる主記憶装置のことで、コンピュータの黎明期にあたる1955年から1975年頃に多用された。原理的に破壊読み出しで、読み出すと必ずデータが消えるため、再度データを書き戻す必要がある[1]:336-337。破壊読み出しだが、磁気で記憶させるため、不揮発性という特徴がある[注 1]。

縦方向、横方向、さらに斜め方向の三つの線の交点にコアを配置する。縦横方向でアドレッシングを行ない、斜め方向の線でデータを読み出す。

歴史[編集]

角形ヒステリシス特性を有するある種の磁性材料をストレージまたはスイッチングデバイスとして利用する、というコンセプト自体は、コンピュータの発明初期より存在した。しかし、磁気コアメモリの発明者とされるのは、アン・ワング、ジャン・A・ライクマン、ジェイ・フォレスターの3人である。

磁気コアメモリを世界で初めて開発したのは上海生まれのアメリカ人物理学者であるアン・ワング(王安)と Way-Dong Woo である。彼らは1949年に「パルス転送制御デバイス」を開発したが、その名称が意味するのはコアの磁場を活用して電気機械式システムの制御をするというものだった。ワングと Woo はハーバード大学のハワード・エイケン計算研究所に勤務していたが、大学側は彼らの発明を売り出すことに興味を持たなかった。そのため、ワングらは自分たちで特許を申請することにした。Wooが病気のため中国に帰国したのち、1955年にワングが米国において単独で特許権を取得したため、ワングが磁気コアメモリの発明者とされる。

RCA社のジャン・A・ライクマンもコアメモリに関する先駆的な研究を行っている。ライクマンはフェライト製のバンドを薄い金属管に巻き付けるという構造のストレージシステムを発明し[2]、アスピリン錠のプレス成型機を転用した機械を使ってこれを実際に製造し、1949年に発表した。しかし、ライクマンはRCA社において当時の次世代メモリの本命と目されていた静電記憶管(electrostatic memory tube。CRTを利用した記憶装置)であるウィリアムス管およびセレクトロン管の開発の中心人物であり、後のコアメモリに繋がる研究はこれだけに終わった[3]。

マサチューセッツ工科大学 (MIT) の Whirlwind プロジェクトに従事していたジェイ・フォレスターらのグループが、このワングらの業績に気づいた。Whirlwind はリアルタイムのフライトシミュレーションに使われる予定であり、高速なメモリを必要としていた。最初はウィリアムス管を使おうとしていたが、このデバイスは気まぐれで信頼性に乏しかった。そのため、MIT放射線研究所が開発中であった双電子銃管(dual-gun electron tube)を採用することにしたが、これは失敗で、何年たっても完成せず、1951年の時点ではウィリアムス管以下の性能で、Whirlwindに要求される性能を満たさなった。アメリカ空軍の防空システムに使用するため、年間約100万ドルと言う莫大な金が投入されているにもかかわらず、メインメモリが遅すぎて使い物にならない状態だったので、ジェイ・フォレスターは代替品を探すのに必死であった。

ふたつの発明によって磁気コアメモリの開発が可能となった。ひとつはアン・ワングのライト-アフター-リード・サイクルの発明である。これにより情報を読み出すと消えてしまうという問題が解決された。もうひとつはジェイ・フォレスターの電流一致システム (coincident-current system) であり、これによって多数のコアを数本のワイヤで制御することが可能となった。こうして1951年に磁気コアメモリの原理が発明された。ジェイ・フォレスターの2年の研究の結果、アクセス時間9マイクロ秒、記憶容量1024ワードという、Whirlwindの要求性能についに到達し、1953年夏、磁気コアメモリがWhirlwindに取り付けられた。これが史上初、コンピュータに実用搭載された磁気コアメモリである[1]:21。当時各所で開発中であった次世代の静電記憶管(前述のMITの双電子銃管、RCA社のセレクトロン管など)が実用化される前に、これを超える性能を持つ磁気コアメモリが実用化されたことにより、静電記憶管の研究は全て中止された。ウィリアムス管を採用していたIBM 702(1953年発売)もすぐに磁気コアメモリを採用したIBM 704(1954年)を発売し、フェランティ社など他のコンピュータ会社もそれに続いた。商用製品としては、ジュークボックスのシーバーグ社が1955年に「Tormatコントロールシステム」として磁気コアメモリを用いた記憶システムを採用し、コンピュータ以外に電話機やその他の産業用機器など非常に広い範囲で採用されるようになった。

磁気コアメモリにおいて最もコストがかかったのは、フェライトコアにワイヤーを張る人件費である。フォレスターの発明した電流一致システムでは、ワイヤの1つをコアに対して45度で走らせる必要があったが、これは機械によるワイヤリングが難しかったため、人間が顕微鏡を見ながら精密なモーター制御を行ってコアの配列を編み上げる必要があった。そのため1950年代後半には、極東でコアメモリ製造工場ができており、例えば東京電気化学工業(現・TDK)の市川工場(東京電気化学工業株式会社電子事業部、現・TDKテクニカルセンター)が1956年に設立されている。日立製作所茂原工場(現・ジャパンディスプレイ)におけるコアメモリの生産開始時期は不明である。工員の多くは「手先が器用」とされた女性で、当初は縫製工が雇われたが、1956年に東京通信工業(現・ソニー)が工員募集の際に「女工」の代わりに使った「トランジスタ娘」のキャッチコピーが話題となったため、それまでの紡績メーカーに代わって電子機器メーカーの工員が女性の花形職業となった。数百人の労働者が一日数セントの賃金でコアメモリを組み立てていた。これによってコアメモリの価格が低くなり、1960年代初めには主記憶装置として広く使われるようになり、低価格/低性能の磁気ドラムメモリも高価格/高性能の静電記憶管(ウィリアムス管など)も使われなくなっていった。「コアメモリプレーン」として1枚だけで使われることもあった(平面実装方式)が、「コアメモリスタック」として何枚も積み重ねて大容量化を図った製品もあった。例えば8K*8Kのプレーンを64枚スタックした3D方式のコアメモリの場合、1スタックで8K*8K*64 = 4096Kの大容量を扱えることになる。ただし、「スタック」の形式をとると発熱や価格などの問題があるため、特にコアメモリの実装密度が向上した1970年代以降は、一般的な計算機ではコアをスタックするよりも平面展開してプレーン1枚だけで使われることが多かった。

コストを抑えるため、半自動化に向けての技術革新が続いた。1956年にIBMのグループが、最初の数本のワイヤーを各コアに自動的に通す装置の特許を申請した。この装置はフェライトコアの平面部分を「ネスト」状に保持し、さらにその後、中空の針の配列をコアに突き通して、ワイヤーを編組む際のガイドとするものである。この装置を使用することで、128 x 128コア(16,384bit)の配列においてX線とY線(縦横のワイヤー)を編組むのにかかっていた時間が、それまでの25時間から12分に短縮された[4][5]。フェライトコアが微細化するに従って、中空の針を使う方式は役に立たなくなってしまった物の、代わりにガイド用の通路が付いた補助ネストが開発された。フェライトコアを「patch」ごとに裏材に接着するようになり、編組時や使用時に便利になった。メモリプレーンを編組するための針をワイヤーに突合せ溶接することで、針の径はワイヤーの径と同じになり、(特許の出願はDRAMの普及より後になるが)針自体を無くすための発明もなされた[6][7]。オートメーション化において重要だったのが、インヒビット線(禁止線)とセンス線(探査線)の編組方式の改良で、これによりセンス線を斜め方向に長々と伸ばす必要が無くなり、また各ブロックにおいてフェライトコアをより密接に配置することも可能となった[8][9]。

磁気コアメモリの製造が自動化されることはなかったが、その価格はほぼムーアの法則に従った推移を示した。最初のころビット当たり1ドル程度だった価格は、最後にはビット当たり0.01ドルになっている。フェライトコアも1950年代には直径0.1インチ(2.5 mm)だったものが、1966年には0.013インチ(0.33 mm)にまで微細化。1967年には台湾でも高雄日立(現・高雄晶傑達光電科技)が設立されてコアメモリの生産を開始する。日本や台湾など極東の人件費の安い国の工場で大量の女工を投入して人の手で編組みするという、典型的な労働集約型の製造方法を取っていた。

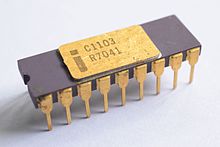

その後磁気コアメモリは 1970年代初めにシリコン半導体のメモリチップ (RAM) に置き換えられていった。特に半導体ベンチャー企業(1968年創業)のIntel社が1970年に発売した世界初のDRAM、Intel 1103(容量1,024bit)は、磁気コアメモリと同等以上の集積度を実現しており、またその1ビット1セントを下回る低価格性もあって(Intelは1969年に容量256bitのSRAMであるIntel 1101を発売していたが、高価だったので磁気コアメモリを置き換えることができなかった)、この発売以後、メインフレームにおいて磁気コアメモリからDRAMへの置き換えが急速に進んだ。Intel社の創業当時のロゴ(通称:ドロップドイー)は、下に下がった「e」がコアメモリを齧る様子を表しており、DRAMはその低コスト性、信頼性、省スペース性によって、文字通りコアメモリのシェアを食う形で普及していった。インテルミュージアム(Intelを記念するカリフォルニアの博物館で、磁気コアメモリも展示されている)の説明によると、1972年にIntel 1103 DRAMのシェアが磁気コアメモリのシェアを上回ったという。1973年から1978年にかけて、末期には生産されるコアメモリのほとんどが保守用パーツだったが、次第に市場が縮小していった。

磁気コアメモリは、磁気をスイッチや増幅に使用する様々な技術のひとつである。1950年代、ウィリアムス管に代表される真空管メモリは先端技術であったが、その材質は壊れやすく、発熱と電力消費が大きく、不安定であった。磁気デバイスはトランジスタなどの半導体デバイスと同様の利点を持っていて、軍事利用された例が多い。

特許問題[編集]

ワング博士の出願した特許は1955年にようやく認められたが、そのころには既に磁気コアメモリが使われていた。そのため長い訴訟問題となったが、1956年にIBMがワングに数百万ドルを支払って特許権を買い取ることで解決した。ワングはこれを資金としてワング・ラボラトリーズの規模を拡大させた。なおワングはこの時の因縁からIBMに対抗意識を燃やし、電卓、ワープロ機、そしてミニコン市場に進出。全盛期となる1980年代初頭にはアメリカのOA機器市場でIBMを上回る市場シェアを誇ったが、IBMが1980年代にはパソコンに力を入れたのとは対照的に、ワングはワープロ機やミニコンなどの独自システムの展開に固執したため、1980年代後半にはアメリカのオフィスにあったワングのOA機器はIBM社のパソコンに置き換えられ、1992年に倒産した。

一方、フォレスターの特許に関してもIBMとMITで訴訟となった。MITは1959年の時点で、1コア当たり2セントの特許料を要求していたが、磁気コアメモリの普及により、1963年度のIBM社の年間報告書におけるフェライトコアの生産量を見る限りでは、その年だけで20万ドルを支払わなければいけない事が判明したため、IBM社が13万ドルを一括で支払うことで1964年にMITと同意。当時としては史上最高額の特許料であった。

フォレスターが2011年に回想したところによると、(一般的には磁気コアメモリの発明者の1人だとされている)ワングの発明は自分の発明に全く何の影響も及ぼしていない、とのこと。フォレスターはコンピューター業界において7年がかりでコンピューターのメモリを磁気コアメモリに置き換えた後、特許裁判所において7年がかりで自分こそが磁気コアメモリの発明者だと認めさせた[10]。

日本における磁気コアメモリの歴史[編集]

1954年、東京大学理学部高橋秀俊研究室の学生であった後藤英一がパラメトロン素子を発明する。同年7月、後藤がパラメトロン素子を日本電信電話公社(現・NTT)電気通信技術委員会研究専門委員会の電子計算機研究専門委員会において発表したところ、これが高く評価され、日本の各所でパラメトロン方式の計算機の開発が始まった。一方同時期、電子計算機研究専門委員会において米国のI.R.E誌(現・IEEE誌)の計算機特集を各委員で手分けして子細に検討していたところ、1954年2月、後藤と高橋は同誌に掲載されていた前述のRCA社のジャン・A・ライクマンの論文を知る。これがたまたまパラメトロンと同じく磁心(フェライトコア)を利用する物であったことと、パラメトロンの高い信頼性に釣り合うメモリと言うことから、高橋はパラメトロン方式の計算機に使用されるメモリとして磁気コアメモリ(当時の日本語では「磁心記憶装置」)を使用することに決定した。このように、日本で磁気コアメモリが次世代メモリの本命とされ、研究開発が開始されたのはかなり早い。当時の電電公社は製造部門を持たなかったため、技術開発はメーカーとの共同によってなされていた。

ただし、パラメトロン方式の計算機では交流が使われるため、直流を用いた米国の磁気コアメモリの方式をそのまま使うことができなかった。そのため、後藤はパラメトロンに適した磁気コアメモリである「二周波メモリ」を発明し、1955年4月に特許を出願し[11]、1956年2月に電子計算機研究専門委員会で発表した。この「二周波メモリ」が1950年代後半の日本のパラメトロン方式の計算機で使われている磁気コアメモリの方式である。パラメトロン方式の計算機で磁気コアメモリが採用されたのは、当時の日本では技術やコストの制約で水銀遅延線や静電記憶管のような既存の装置を開発するのは困難だという消極的な理由もあったが、後藤ら開発者がその可能性を正しく評価できたことと、東京電気化学工業(TDK)の協力が得られたことが大きな理由である[12]。

後藤はフェライトコアの制作をTDKに依頼した。後藤によると、パラメトロン用のフェライトコアの制作に関しては、最初に作った銅・亜鉛系のコアがたまたまパラメトロンに最適な物で、ラッキーだったが、磁気コアメモリ用のフェライトコアの制作に関してはものすごく苦労したとのこと[13]。これが取り付けられたパラメトロン計算機PC-1が日本初の磁気コアメモリを採用した計算機となるはずであったが、東京大学高橋研究室によるPC-1本体の開発は難航し、稼働したのは1958年3月となった。結局、後藤のアイデアに基づいて電電公社の電気通信研究所(通研、現・NTT武蔵野研究開発センタ)が後から開発し、1957年3月に稼働したパラメトロン式計算機MUSASINO-1が最も早かった。ただし、MUSASINO-1の当初のコアメモリの記憶容量はたった32ワード(1280ビット)であり、1958年3月に256ワード(10,240ビット)に拡張されてようやく実用的になった。

電電公社の主導するパラメトロン計算機の流れは続かず、日本メーカー各社は1950年代後半より米国メーカーと提携して、米国より日本に計算機の技術移転が開始される。

日本が「世界の工場」として海外向けの磁気コアメモリを作っていた歴史は前記を参照。ただし、単に米国メーカーの技術をベースに安価なコアメモリを提供するだけだったわけではなく、TDKや日立など日本メーカーの独自の発明もいくつかなされており、米国特許も取得している。当時生産された物のいくつかは産業遺産として保存されており、例えば日立製作所が1964年にHITAC 5020用に制作した4Kの磁心記憶装置が日立製作所に所蔵されているほか、NTT技術史料館に所蔵されているMUSASINO-1にも磁心記憶装置が搭載されている。4Kのコアメモリで1ユニット当たり4096個、64K(8K*8K)の物で65536個も搭載されたフェライトコアは、全て顕微鏡を見ながらドーナツ状のフェライト磁石(リングコア)に銅線を1本ずつ手で通したものである。

なお、コアメモリは人件費の安い日本の工場で製造することで低価格化を図り、メインメモリとして磁気ドラム装置などに代わって広く普及させることに成功したが、それでも高価であることには変わりなかった。特に日本国内の組織が自前でコンピュータを作る際はTDKや日立に高い金を払ってコアメモリを購入することになるため、例えば電電公社・日本電気(NEC)・日立製作所・富士通の4社共同で1968年より開発が開始された電電公社のDIPS-1(主記憶16MB)では、磁気コアメモリがそのセンタコストの約3割を占めたという[14]。そのため、DIPS-1では後にコアメモリより安くて大容量な磁気ドラム装置を用いた仮想記憶システムが搭載された。磁気ドラム装置は安価で大容量と言う点を生かし、1960年代以降には補助記憶として利用されるようになったが、メインメモリのコアメモリと比べると1000倍程度遅く、1970年当時には主記憶と補助記憶のあまりに大きすぎる性能差が問題となっていた。電電公社のシステムでは従来の固定ヘッドに代わって浮動ヘッド方式を採用することで10倍の高速化を成し遂げたが、それでも遅かった。

日本メーカーが半導体メモリの量産を開始するのは、Intelの2年後となる1973年頃からである。NEC(半導体事業部、後に日立の半導体事業部と合併、現・マイクロンメモリジャパン)の開発したSRAMは1973年にDIPS-1に搭載された(NECは1968年に144bitのSRAMを開発していたという説がある[15])。また、日立製作所(半導体事業部、現・マイクロンメモリジャパン)も1973年に日立初の半導体メモリとなるHM3503シリーズ(1,024ビット、Intel1103シリーズ相当品)の量産を開始する。コアメモリは信頼性、コスト、電源を切っても記憶内容が消失しないなど、1973年の時点でも半導体メモリに対する利点は依然として大きく、メインメモリ以外の分野ではしばらくはコアメモリを置き換えることは無いだろうというのが業界の予想であり、日立の社内誌である『日立評論』においても1973年以後もいくつかコアメモリの高性能化に向けた論文が発表されているが、一方で、大容量、速度、コストの面から今後の半導体メモリの市場性が高いことに日立は気づいていた[16]。日立は1952年にRCA社と技術提携し、日立製作所茂原工場(現・ジャパンディスプレイ)にRCA社の技術導入を行った際「欧米との20年の技術的な隔たり」[17]があると語ったが、20年後の1972年の時点では世界の半導体ビッグスリーの一角を占めるまでになっていた。

なお、国際電信電話(KDD、現・KDDI)の大島信太郎らが、RCA社のライクマンの特許をベースにパラメトロン用の磁性薄膜メモリを1960年頃に開発している[18]。大島らの開発した磁性薄膜メモリの方式は、電着法によって銅線表面に磁性合金膜を析出した磁性線(ワイヤ)を記憶素子として利用した、織成形ワイヤメモリの一種である。「磁性薄膜メモリ」とは、磁性薄膜を平板(プレート)もしくは磁性線(ワイヤ)にめっき、電着、蒸着などの方式で形成して記憶素子としたもので、コアメモリと同等の特性を持ちながら、コアを人の手で編組しているコアメモリと比較して量産性・高密度性・高速性に優れていると考えられており、1950年代後半より各所で試作されていたが、1960年代以降のコアメモリの(依然として人の手で編組しているにもかかわらず)想像以上の微細化・高速化・低価格化・大容量化と、薄膜の不安定さなど技術開発の困難さにより、学術機関や軍関係など特殊な機関における採用に留まり、米国においても商用化はなされていなかった。しかし大島らはこれらの問題を解決する「ファインストライプトメモリ」を開発[19](これにより1971年度の電子通信学会業績賞を受賞)。コアメモリは1960年代後半ごろにはフェライトコアの微細化の限界に由来する問題から、1966年に直径14ミル(0.35 mm)に到達して以来微細化がストップしていたため、いよいよ「機は熟した」ということで、「ファインストライプトメモリ」の技術はコアメモリに代わる次世代メモリとして日本の主要メーカー13社に技術指導がなされ、1970年頃には東光(現・埼玉村田製作所)が量産化にまでこぎつけたが[20]、この後すぐに半導体メモリの量産が開始されたためにあまり生産されなかった。なおフェライトの微細化に関しては、HITAC 5020を開発した日立の村田健郎によると、「女工さんの目が潰れるので、これ以上は無理」だったとのこと(図書館情報大学教授時代の村田が、教え子である阪口哲男に語ったところによる[21])。

TDKは2020年現在もまだフェライトコアを作っている。リングコアを自力で編組することで磁気コアメモリの自作も可能。2021年現在、数寄者が製作したarduino用のコアメモリモジュール(容量:32ビット)が市販されている。

構造と記憶の原理[編集]

一般的な磁気コアメモリについて、その構造と記憶の原理について説明する。

基本的な要諦は、フェライトコアの特性としてその磁化特性について、ヒステリシスの存在により着磁の変化に一定の「しきい値」のようなものがあることである。

磁気コアメモリは、小型のフェライト磁性体のリング(コアという)に電線が通されたものが、格子状に多数配置された構造になっている。コアの一つが1ビットの記憶容量を持つ。

一つのコアに対しては、書き込み用電線が縦横の各1本で2本、それと読み出し用電線1本が通っている。書き込み用電線は格子状に配線され格子点にコアがある。格子の縦横各1本の書き込み用電線を指定すると、一つのコアが定まるわけである。これがビットアドレスの指定になる。縦と横のそれぞれ1本の電線に流す電流は、ある程度の余裕を持って前述のしきい値よりも低い磁力しか発生させない程度に流す。これにより、交点にある、両方の電線が通っている唯一のコアだけが十分な強さの磁力の変化を受ける。

あるコアにデータを書き込むには、そのコアに対応する書き込み用電線2本に電流を流して磁化させる。電流の方向によりコアの磁界の向きが決まり、それにより0か1のビット値が決まる。なお、磁化されたコアは、電流が止まっても磁化した状態を保持するので不揮発性のメモリということができる。

あるコアのデータを読み出すには、そのコアに対応する書き込み用電線2本に電流を流し、読み出し用電線の電流を検知する。このとき現在のコアの磁界の向きが逆転するようであれば、読み出し用ケーブルに電流が流れる。逆転しない場合は、読み出し用電線に電流が流れない。これによりコアのビット値が判明する。しかし、データを読み出すときに、書き込み用電線2本に電流を流すのでコアが磁化されてしまい、読み出し前の内容が失われてしまう(非破壊読み出しができない)。このためコアの内容をその後も保持したい場合は、「書き戻し」が必要である。

豆知識[編集]

- コンピュータのメモリが半導体化されて久しいが、メモリ内容をダンプしたファイルをコアダンプ(プログラムの異常終了などでそうなることを「コアを吐く」ともいう)と呼ぶのは磁気コアメモリが使われていた当時の名残りであり、現在でも使われている。

- IBMは半自動式防空管制組織に用いた磁気コアメモリの駆動回路に、真空管に代えてシリコントランジスタを採用し信頼性と高速性を確保した。トランジスタがゲルマニウム製全盛期に、シリコントランジスタを製造できたのはロバート・ノイス率いるフェアチャイルドセミコンダクターのみであり、IBMはフェアチャイルドセミコンダクターから独占的に高額で買い付け、創業時のフェアチャイルドセミコンダクターを(結果的に)資金面で支えた。後年フェアチャイルドセミコンダクターを見限ったロバート・ノイスは、半導体メモリを集積回路で安価に製造することで、(自身が普及を助けた)磁気コアメモリに取って代わることを目的としてインテルを設立した。最初期の社章はコアを齧るイメージを用いている。最初のD-RAMを商品化したのもIntel社である。

- 最も遅い時代までコアメモリが使われていたとしてよく語られるもののひとつに、スペースシャトルの飛行制御システムに使われたAP-101の初期型がある。このことはファインマンの逸話集『困ります、ファインマンさん』に書かれて広く知られるようになった[22]。

- 特定のコアへのアクセスが集中すると、そこが熱を持って正常動作が出来なくなる。これは、プログラムで同一変数に連続して操作を行うと値が化ける現象として現れる。そのため、プログラムでは異なる変数を順次操作する様に考慮する必要がある。

脚注[編集]

注釈[編集]

出典[編集]

- ^ a b P.HAYES, JOHN (1978,1979). Computer Architecture and Organization. ISBN 0-07-027363-4

- ^ Jan A. Rajchman, Magnetic System, アメリカ合衆国特許第 2,792,563号, granted May. 14, 1957

- ^ Hittinger, William (1992). “Jan A. Rajchman”. Memorial Tributes (US: National Academy of Engineering) 5: 229.

- ^ Walter P. Shaw and Roderick W. Link, Method and Apparatus for Threading Perforated Articles, アメリカ合衆国特許第 2,958,126号, granted Nov. 1, 1960.

- ^ Bashe, Charles J.; Johnson, Lyle R.; Palmer, John H. (1986). IBM's Early Computers. Cambridge, MA: MIT Press. pp. 268. ISBN 0-262-52393-0

- ^ Robert L. Judge, Wire Threading Method and Apparatus, アメリカ合衆国特許第 3,314,131号, granted Apr. 18, 1967.

- ^ Ronald A. Beck and Dennis L. Breu, Core Patch Stringing Method, アメリカ合衆国特許第 3,872,581号, granted Mar. 25, 1975.

- ^ Creighton D. Barnes, et. al., Magnetic core storage device having a single winding for both the sensing and inhibit function, アメリカ合衆国特許第 3,329,940号, granted July 4, 1967.

- ^ Victor L. Sell and Syed Alvi, High Density Core Memory Matrix, アメリカ合衆国特許第 3,711,839号, granted Jan. 16, 1973.

- ^ Kleiner, Art (2009年2月4日). “Jay Forrester's Shock to the System”. The MIT Sloan Review. 2018年4月1日閲覧。

- ^ アメリカ合衆国特許第 2946045A号,Digital memory system ,Goto Eiichi

- ^ 「パラメトロン用記憶装置の開発」、小山俊士、哲学・科学史論叢 第十八号、東京大学、2016年

- ^ パラメトロン計算機pc-1 - 後藤英一

- ^ 2016/3/10 DIPS4150形磁気ドラム記憶装置が「情報処理技術遺産」に認定されました。 - NTT技術史料館

- ^ 【福田昭のセミコン業界最前線】Intelの歴史を「インテルミュージアム」から振り返る【メモリ編】 - PC Watch

- ^ 『日立評論』1974年1月号p.48

- ^ 『日立評論』1952年11月号、p.101

- ^ アメリカ合衆国特許第 3381138A号

- ^ 発見と発明のデジタル博物館: 磁性薄膜メモリの発明開発 (専門向け)

- ^ ワイヤメモリーシステム - 電通大 UEC コミュニケーション ミュージアム所蔵

- ^ 阪口哲男のtwitter 2020年8月1日

- ^ 「ジョンソン基地では非常に良いソフトウェアを作っているのだが、悲しいかなシャトルに載っているコンピュータは、およそカビでも生えそうな時代遅れのモデルで、もう製造すらしていない。その記憶装置も中に電線が通った磁気コアから成るおよそ旧式なしろものだ。」R.P.ファインマン『困ります、ファインマンさん』〈岩波現代文庫〉2001年、278頁。ISBN 9784006030292。

関連項目[編集]

外部リンク[編集]

- 第94回「磁気記録の技術史」の巻 - TDKによる磁気コアメモリ(3D4W式)の仕組み

- HITAC 5020および関連部品 - 情報処理学会のコンピュータ博物館によるHITAC 5020の磁気コアメモリ(日立製)の紹介

いずれも英文